# **WELCOME TO ESSDERC 2010**

On behalf of the Organizing Committees of ESSDERC 2010, it is our pleasure to welcome you to the 40th European Solid-State Device Research Conference. ESSDERC 2010 runs parallel to his sister conference ESSCIRC 2010, covering all aspects of modern solid-state systems, circuits and devices at a single event. In combination, these two conferences provide a unique forum where technologists, device experts, and circuit and system designers can interact. This interaction is instrumental to fully exploiting the potential of modern devices and technologies when confronting the challenges of system-on-chip (SoC) integration. As a delegate at ESS-DERC-ESSCIRC 2010 you will have the opportunity to learn of the latest advances in these fields, and to meet those who have dared, pioneered, and succeeded.

The conferences are to be held at the Barceló Hotel Renacimiento, on the Isla de la Cartuja, an island located between two branches of the Guadalquivir river which today is home to the Cartuja 93 technology business park. Seville's downtown (El Centro) is very close by and, from there, visitors will find Seville's major monuments and shops just a few short steps away.

This year, a total of 193 submissions originating from 29 countries were received for ESSDERC including 129 papers coming from Europe, 39 from Asia-Pacific, 15 from North America and 10 from the Middle East and Africa. This is proof of the truly international nature of ESSDERC. The Technical Program Committee with about 110 world-class experts from academia and industry selected 95 papers for oral presentation. Twelve plenary presentations by guest speakers complete the program by focusing on highly relevant topics selected by the Technical Program Committees of both conferences. In addition to the conference programs, a pre-conference day with introductory tutorials and a post-conference day with workshops showcasing work currently being carried out by European research consortia will also be held.

We would like to thank the Steering Committee of ESSDERC-ESSCIRC for giving us the opportunity to organize this event.

# **WELCOME TO ESSDERC 2010**

The meeting has been organized by members of the Institute of Microelectronics of Seville (CNM-CSIC), the University of Seville and the University of Granada. We would like to thank the authorities of these institutions for allowing us to devote part of our time to the organization.

We have been extremely fortunate to have the help of an outstanding team of volunteers of the Organizing Committee and the Technical Program Committee, who have all worked very hard. We are hugely indebted to all these volunteers. Our warm thanks to all of them for their dedication, enthusiasm and professionalism.

Last but not least, we would like also to express our greatest appreciation to all the authors who submitted papers to the conference and to all delegates, tutorial lecturers and plenary speakers who have travelled to Seville to interact and share their thoughts during the Conference. They will play a leading role at the event.

Enjoy ESSDERC-ESSCIRC 2010 and your visit to Seville. We hope to see you all back here more often!

Welcome / Bienvenidos!!

José L. Huertas Ángel Rodríguez-Vázquez General Chairs - ESSDERC-ESSCIRC 2010

# **ABOUT UNIV. OF GRANADA**

The Universidad de Granada, founded in 1531, continues a long teaching tradition, the roots of which can be traced back to the madrasahs of the last Nasrid Kingdom.

The University is a vibrant presence in the city of Granada, benefiting from the distinctive beauty of its environment and a privileged geographical location due to its proximity to the Sierra Nevada, an excellent ski resort and the Mediterranean coast, with several major tourist sites, including Motril, Almuñécar and Salobreña.

In Granada, there are four University Campuses, as well as the "Campus Centro", in which all the centres spread throughout the historic part of the city are brought together. The UGR's policy of using buildings of historical and cultural value has enriched its heritage, as well as promoting the restoration and maintenance of these buildings. In addition to this emphasis on more traditional elements, the Health Science Technological Park, which is still being developed, demonstrates our strong commitment to innovation by promoting interaction with technological bio-health companies and favouring high-quality healthcare and biomedical knowledge. There are two other UGR Campuses in the cities of Ceuta and Melilla, in Northern Africa.

Over 60,000 undergraduate and postgraduate students study at the UGR, with another 20,000 students taking additional courses, language courses, summer courses etc. The University employs 3650 lecturers and over 2000 administration, technical and maintenance staff.

At present, courses for 75 different qualifications are taught in the 28 teaching centres of the UGR. The courses are taught across 116 departments. The Postgraduate School offers 68 master's courses, 116 doctorate programmes and 113 additional courses.

The commitment to high-quality research has placed the Universidad de Granada in a prominent position in terms of national rankings. The financing of 346 research groups illustrates this commitment. Through the Spanish Research Programme, as well as other national programmes and organisations, the University supports 165 research projects, and the Ministry of Innovation, Science and Business has provided financial support to a high number of Projects of Excellence.

For many years, the UGR has promoted a significant international activity through the Vice-Rector's Office for International Relations.

# **ABOUT UNIV. OF GRANADA**

The importance of the presence of international students is most clearly demonstrated by the 606 mobility agreements signed with European Higher Education institutions and the ERASMUS mobility programmes; the UGR is the leading European university in terms of receiving students and the second Spanish university in terms of the mobility of its own students.

The University is also involved in major exchange programmes with universities in the United States, Canada, Latin America, Central and Eastern Europe, the Middle East, Mediterranean countries, Australia, Oceania and Asia.

About IMSE/University of Sevilla (please see ESSCIRC Programme, page 3).

| ESSDERC Schedule                                                  | 6  |

|-------------------------------------------------------------------|----|

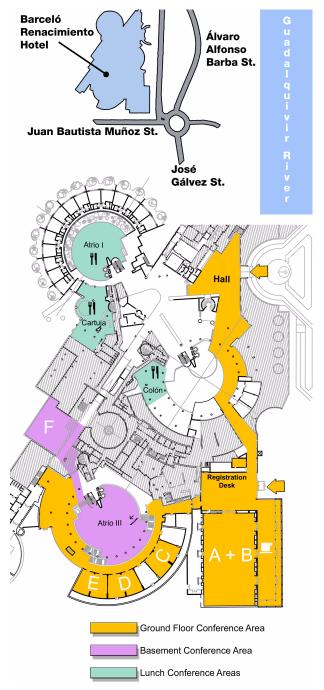

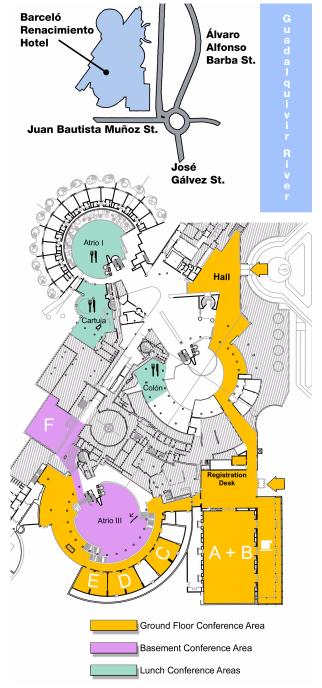

| Meeting Rooms Floorplan                                           | 8  |

| Programme at a glance                                             | 9  |

| Committees                                                        | 12 |

| Welcome to Sevilla<br>(see ESSCIRC Programme, pages 18-22)        |    |

| Conference Venue<br>(see ESSCIRC Programme, pages 23-28)          | 20 |

| Conference Information<br>(see ESSCIRC Programme, page 29)        |    |

| Conference Overview                                               | 21 |

| Meals and Refreshments<br>(see ESSCIRC Programme, page 33)        |    |

| Social Programme<br>(see ESSCIRC Programme, page 34)              |    |

| Optional Leisure Activities<br>(see Program ESSCIRC, pages 35-37) |    |

| Joint Plenary Talks<br>(see ESSCIRC Programme, pages 38-44)       |    |

| ESSDERC Plenary Talks                                             | 24 |

| ESSDERC Tutorials                                                 | 28 |

| ESSDERC Programme                                                 | 30 |

| ESSDERC Workshops                                                 | 54 |

| ESSDERC Fringe                                                    | 62 |

# **ESSDERC SCHEDULE**

SSDERC SCHEDULE

# Monday, September 13th, 2010

**Tutorials**

Rooms C, D, E, F

# Tuesday, September 14th, 2010

8:30 Conference Opening

# **Technical Sessions**

| 9:00  | Joint Plenary Lecture          |

|-------|--------------------------------|

| 9:50  | Joint Plenary Lecture          |

| 10:40 | Coffee Break                   |

| 11:00 | Fringe Poster Briefing Session |

| 11:20 | ESSDERC Sessions               |

| 13:00 | Lunch                          |

| 14:20 | Fringe Poster Briefing Session |

| 14:50 | ESSDERC Sessions               |

| 15:50 | ESSDERC Plenary Lecture        |

|       |                                |

16:50 Coffee Break

17:20 ESSDERC Sessions

18:40 Fringe Poster Briefing Session

# **Welcome Reception**

# Wednesday, September 15th, 2010

# **Technical Sessions**

| 9:00  | Joint Plenary Lecture   |

|-------|-------------------------|

| 9:50  | Joint Plenary Lecture   |

| 10:40 | Coffee Break            |

| 11:20 | ESSDERC Sessions        |

| 13:00 | Lunch                   |

| 14:50 | ESSDERC Sessions        |

| 15:50 | ESSDERC Plenary Lecture |

| 16:50 | Coffee Break            |

| 17:20 | ESSDERC Sessions        |

|       |                         |

# **Gala Dinner**

# Thursday, September 16th, 2010

# **Technical Sessions**

| 9:00  | Joint Plenary Lecture |

|-------|-----------------------|

| 9:50  | Joint Plenary Lecture |

| 10:40 | Coffee Break          |

| 11:20 | ESSDERC Sessions      |

# **ESSDERC SCHEDULE**

Lunch 13:00 14:50 **ESSDERC Sessions ESSDERC Plenary Lecture** 15:50 16:50 Coffee Break **ESSDERC Sessions** 17:20 Friday, September 17th, 2010

Workshops Rooms C, D, E, F

# **MEETING ROOMS FLOORPLAN**

# PROGRAMME AT A GLANCE

# PROGRAMME AT A GLANCE

| Tuesday Se                           | Tuesday September 14th, 2010                                           |                                                                                                                                                               |                                                                                                                                                                    |                                                                |                                                                                                                                          |                                                                                                                                                          |

|--------------------------------------|------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| Time                                 | ROOM B                                                                 | ROOM E                                                                                                                                                        | ROOM D                                                                                                                                                             | ROOM A                                                         | ROOM C                                                                                                                                   | ROOM F                                                                                                                                                   |

| 8:30                                 |                                                                        | CONFERENCE OPENIN                                                                                                                                             | CONFERENCE OPENING (Prof. Ángel Rodríguez-Vázquez and Prof. José Luís Huertas) ROOM A+B                                                                            | and Prof. José Luís Huertas                                    | ) ROOM A+B                                                                                                                               |                                                                                                                                                          |

| 09:00-09:20                          |                                                                        | JOINT PL                                                                                                                                                      | A11A (ROOM A+B) JOINT PLENARY: High Performance Mixed Signal - Business and Technology SPEAKER: Dr. Rene Penning de Vries (NXP)                                    | .+B)<br>ignal - Business and Techr<br>g de Vries (NXP)         | ıology                                                                                                                                   |                                                                                                                                                          |

| 09:50-10:40                          |                                                                        | JOINT PLEN.                                                                                                                                                   | A2L-A (ROOM A+B) JOINT PLENARY: 3D Integration Technology: Status and Application Development SPEAKER: Dr. Peter Ramm (Fraunhofer IZM Munich Division)             | (+B)<br>atus and Application Deve<br>ofer IZM Munich Division) | lopment                                                                                                                                  |                                                                                                                                                          |

| 10:40-11:00                          |                                                                        |                                                                                                                                                               | COFFEE BREAK                                                                                                                                                       |                                                                |                                                                                                                                          |                                                                                                                                                          |

| 11:00-11:20                          |                                                                        |                                                                                                                                                               | FRINGE POSTER BRIEFING SESSION                                                                                                                                     | SESSION                                                        |                                                                                                                                          |                                                                                                                                                          |

| 11:20-13:00 A3L-B<br>Proces<br>Moore | A3L-B<br>Process Integration: More than<br>Moore Devices Architectures | A3L-C<br>Reliability, variability and<br>mismatch                                                                                                             | A3L-D<br>SRAM and DRAM                                                                                                                                             | A3L-F<br>Analog Voltage<br>References                          | A3L-G<br>Imagers                                                                                                                         | A3L-H<br>RF Frequency Synthesis                                                                                                                          |

| 13:00-14:20                          |                                                                        |                                                                                                                                                               | LUNCH                                                                                                                                                              |                                                                |                                                                                                                                          |                                                                                                                                                          |

| 14:20-14:50                          |                                                                        |                                                                                                                                                               | FRINGE POSTER BRIEFING SESSION                                                                                                                                     | SESSION                                                        |                                                                                                                                          |                                                                                                                                                          |

| 14:50-15:50 A4L-B<br>Altern          | A4L-B<br>Alternative FETs                                              | A4L-C<br>Special characterization<br>methods and structures                                                                                                   | A4L-D<br>Advances in algorithms and<br>simulation methods                                                                                                          | ESSCIRC PLENARY: Terah<br>SPEAKER: Dr. UII                     | A4L-A (ROOM A) PLENARY: Terahertz Imaging with CMOS/BiCMOS Process Tech SPEAKER: Dr. Ullrich Preiffer (University of Wuppertal, Germany) | A4L-A (ROOM A) ESSCIRC PLENARY: Terahertz Imaging with CMOS/BICMOS Process Technologies SPEAKER: Dr. Ullrich Pfeiffer (University of Wuppertal, Germany) |

| 15:50-16:50                          |                                                                        | A5L-A (ROOM B) SDERC PLENARY: Galvon-Si Technology, A New Approach for Advanced Devi SPEAKER: Dr. Tomás Palacios (Massachusetts Institute of Technology, USA) | A5L-4 (ROOM B) ESSDERC PLENARY: GaN-on-Si Technology, A New Approach for Advanced Devices SPEAKER: Dr. Tomás Palacios (Massachusetts Institute of Technology, USA) | A5L-F<br>Amplifiers I                                          | A5L-G<br>Micropower AD<br>interfaces                                                                                                     | A5L-H<br>mm-Wave Transceivers                                                                                                                            |

| 16:50-17:20                          |                                                                        |                                                                                                                                                               | COFFEE BREAK                                                                                                                                                       |                                                                |                                                                                                                                          |                                                                                                                                                          |

| 17:20-18:40 A6L-B                    | A6L-B<br>Soi Mosfets                                                   | A6L-C<br>Ferromagnetic and<br>polycrystalline devices                                                                                                         | AGL-E<br>Cryptographic Processors                                                                                                                                  | AGL-F<br>SAR ADCs and DACs                                     | A6L-G<br>Power Management                                                                                                                | A6L-H<br>mm-Wave Frequency<br>Generation                                                                                                                 |

| 18:40-19:50                          |                                                                        |                                                                                                                                                               | FRINGE POSTER BRIEFING SESSION                                                                                                                                     | SESSION                                                        |                                                                                                                                          |                                                                                                                                                          |

| 21:00                                |                                                                        |                                                                                                                                                               | WELCOME RECEPTION                                                                                                                                                  | NO                                                             |                                                                                                                                          |                                                                                                                                                          |

|                                      |                                                                        |                                                                                                                                                               |                                                                                                                                                                    |                                                                |                                                                                                                                          |                                                                                                                                                          |

# PROGRAMME AT A GLANCE

# PROGRAMME AT A GLANCE

Wednesday September 15th, 2010

| Time                                  | ROOM B                                                            | ROOM E                                                                                                                          | ROOM D                                                                                                                                                           | ROOM A                                                              | ROOM C                                                                                                           | ROOM F                                                                                                                               |

|---------------------------------------|-------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|

| 09:00-09:50                           |                                                                   | JOINT PLEI<br>SPEAKE                                                                                                            | B1L-A (ROOM A+B) JOINT PLENARY: Engineering Hope with Biomimetic Microelectronic Systems SPEAKER: Dr. Wentai Liu (University of California Santa Cruz UCSC, USA) | 4+B)<br>mimetic Microelectronic Sys<br>Ilifornia Santa Cruz UCSC, U | stems<br>SA)                                                                                                     |                                                                                                                                      |

| 09:50-10:40                           |                                                                   | JOI<br>SPEAKER                                                                                                                  | B2L-A (ROOM A+B) JOINT PLENARY: Energy Harvesting - from Devices to Systems SPEAKER: Dr. Yiannos Manoli (IMTEK - University of Freiburg and HSG-IMIT)            | 4+B)<br>from Devices to Systems<br>rersity of Freiburg and HSG-     | IMIT)                                                                                                            |                                                                                                                                      |

| 10:40-11:20                           |                                                                   |                                                                                                                                 | COFFEE BREAK                                                                                                                                                     |                                                                     |                                                                                                                  |                                                                                                                                      |

| 11:20-13:00 B3L-B<br>Simula<br>device | B3L-B<br>Simulation of advanced silicon Photodetectors<br>devices | B3L-C<br>Photodetectors                                                                                                         | B3L-D<br>Silicon and Gallium Nitride<br>power devices                                                                                                            | B3L-F B3L-G TDCs and Timing Circuits Sensors                        | B3L-G<br>Sensors                                                                                                 | B3L-H<br>Power Amplifiers                                                                                                            |

| 13:00-14:50                           |                                                                   |                                                                                                                                 | LUNCH                                                                                                                                                            |                                                                     |                                                                                                                  |                                                                                                                                      |

| 14:50-15:50 B4L-B Modeli stress       | B4L-B<br>Modeling of temperature and<br>stress impacts            | B4L-C<br>Advanced FET<br>characterization                                                                                       | B4L-D<br>Phase Change Memories                                                                                                                                   | ESSCIRC PLENARY: Anale SPEAK                                        | B4L-A (ROOM A) f: Analog Mixed-Signal Circuits in Advanced Technology SPEAKER: Dr. Ian Young (Intel Corporation) | B4L-A (ROOM A) ESSCIRC PLENARY: Analog Mixed-Signic Circuits in Advanced Nano-scale CMOS SPEAKER: Dr. I an Young (Intel Corporation) |

| 15:50-16:50                           | ESSDERC PLEN<br>SPEAKER: Dr. I                                    | B5L-A (ROOM B) ESSDERC PLENARY: High Power LEDs for Solid State Lighting SPEAKER: Dr. Berthold Hahn (Osram Opto Semiconductors) | Vid State Lighting<br>Semiconductors)                                                                                                                            | B5L-F<br>Amplifiers II                                              | B5L-G<br>Circuits for Implantable mm-Wave Receivers<br>Devices                                                   | B5L-H<br>mm-Wave Receivers                                                                                                           |

| 16:50-17:20                           |                                                                   |                                                                                                                                 | COFFEE BREAK                                                                                                                                                     |                                                                     |                                                                                                                  |                                                                                                                                      |

| 17:20-18:40 B6L-B<br>Leakag           | B6L-B<br>Leakage current and traps                                | B6L-C<br>Tunneling FET devices                                                                                                  | B6L-E<br>Memories                                                                                                                                                | B6L-F<br>Pipeline ADCs                                              | B6L-G Biomedical Applications RF Building Blocks                                                                 | B6L-H<br>RF Building Blocks                                                                                                          |

| 21:00                                 |                                                                   |                                                                                                                                 | GALA DINNER                                                                                                                                                      |                                                                     |                                                                                                                  |                                                                                                                                      |

# PROGRAMME AT A GLANCE

Thursday September 16th, 2010

| Time                         | ROOM B                                                                                                                                               | ROOM E                                                                  | ROOM D                                                                                                                            | ROOM A                                               | ROOM C                                                                                                       | ROOM F                                                                                                                                                                                                          |

|------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 09:00-09:20                  |                                                                                                                                                      | JOINT PLEA                                                              | C1L-A (ROOM A+B) JOINT PLENARY: Technical and Economical Trends in Wireless Applications SPEAKER: Dr. Martin Zander (ST Ericsson) | rB)<br>Frends in Wireless Applica<br>r (ST Ericsson) | tions                                                                                                        |                                                                                                                                                                                                                 |

| 09:50-10:40                  |                                                                                                                                                      | JOINT PLEY                                                              | C2L-A (ROOM A+B) JOINT PLENARY: FDSOI: From Materials to Devices and Circuit Applications SPEAKER: Dr. Carlos Mazuré (SOITEC)     | rB)<br>evices and Circuit Applica<br>uré (SOITEC)    | tions                                                                                                        |                                                                                                                                                                                                                 |

| 10:40-11:20                  |                                                                                                                                                      |                                                                         | COFFEE BREAK                                                                                                                      |                                                      |                                                                                                              |                                                                                                                                                                                                                 |

| 11:20-13:00 C3L-B<br>Nanow   | C3L-B<br>Nanowire Transistors                                                                                                                        | C3L-C<br>Device steep slope and<br>leakage                              | C3L-D<br>Advanced Memories                                                                                                        | C3L-F<br>Oversampled ADCs                            | C3L-G<br>DC/DC Converters                                                                                    | C3L-H<br>Wireless Communications                                                                                                                                                                                |

| 13:00-14:50                  |                                                                                                                                                      |                                                                         | LUNCH                                                                                                                             |                                                      |                                                                                                              |                                                                                                                                                                                                                 |

| 14:50-15:50                  | 14:50-15:50 C41-B<br>Channel and Gate Stack<br>Engineering                                                                                           | C4L-C<br>Simulation of III/V devices                                    | C4L-D<br>Charge Trap NAND Flash                                                                                                   | ESSCIRC PLENARY: Ultra I<br>SPEAKER: Dr. David Ruff  | C4L-A (ROOM A) ow Power and Miniaturize and WSN Applications ieux (Swiss Center for Elect CSEM, Switzerland) | C4L-A (ROOM A) ESSCIRC PLENARY: Ultra Low Power and Miniaturized MEMS-based Radio for BAN and WSN Applications SPEAKER: Dr. David Ruffieux (Swiss Center for Electronics and Microtechnology CSEM, Switzerland) |

| 15:50-16:50                  | C5L-A (ROOM B) ESSDERC PLENARY: Trends & Perspectives for Electrical Characterization & Reliability Assessment SPEAKER: Dr. Guido Groeseneken (IMEC) |                                                                         | C5L-E<br>Emerging Memories                                                                                                        | C5L-F<br>mm-wave radar and<br>imaging                |                                                                                                              | C5L-H<br>UWB Communications                                                                                                                                                                                     |

| 16:50-17:20                  |                                                                                                                                                      |                                                                         | COFFEE BREAK                                                                                                                      |                                                      |                                                                                                              |                                                                                                                                                                                                                 |

| 17:20-18:40 C6L-B<br>Analyti | C6L-B<br>Analytical/compact models                                                                                                                   | C6L-C Electromechanical Devices Circuit Design in Emerging Tachnologies |                                                                                                                                   | CGL-F<br>Signal Processing                           |                                                                                                              | C6L-H<br>Optical Communications                                                                                                                                                                                 |

# PROGRAMME AT A GLANCE

# **COMMITTEES**

# **ORGANIZATION COMMITTEE**

Conference Chairs José L. Huertas Díaz

IMSE-CNM-CSIC

Ángel Rodríguez-Vázquez

IMSE-CNM-CSIC

Ángel Rodríguez-Vázquez

IMSE-CNM-CSIC

Manuel Delgado-Restituto

ESSCIRC TPC Chairs IMSE-CNM-CSIC

Karin Halonen

Helsinki University of Tech-

nology

Francisco Gámiz

University of Granada

ESSDERC TPC Chairs Andrés Godoy

University of Granada Michael Östling, Royal Ins.

Tech./KTH

Tutorials & Workshops

Chairs

Manuel Delgado-Restituto

IMSE-CNM-CSIC Andrés Godoy

University of Granada

# **LOCAL ORGANIZATION COMMITTEE**

### CONFERENCE VENUE CHAIRS

Dr. Ricardo Carmona, IMSE-CNM-CSIC

Dr. Santiago Sánchez-Solano, IMSE-CNM-CSIC Dr. Carlos Sampedro, University of Granada

## COMPUTER AND COMMUNICATION INFRASTRUCTURE

# & ADVERTISING CHAIRS

Dr. Gustavo Liñán-Cembrano, IMSE-CNM-CSIC

Dr. Rafael Castro-López, IMSE-CNM-CSIC

Dr. Noel Rodríguez, University of Granada

## **PUBLICATION CHAIRS**

Dr. Oscar Guerra, IMSE-CNM-CSIC / University of Sevilla

Prof. Francisco Jiménez, University of Granada

Prof. Gloria Huertas, IMSE-CNM-CSIC / University of Sevilla

Prof. Rocío del Río, IMSE-CNM-CSIC / University of Sevilla

### LOCAL ARRANGEMENT CHAIRS

Prof. Diego Vázquez, IMSE-CNM-CSIC / University of Sevilla

Prof. Carlos Sampedro, University of Granada

Dr. Piedad Brox, IMSE-CNM-CSIC / University of Sevilla

# **FINANCE CHAIR**

Prof. Antonio Acosta, IMSE-CNM-CSIC / University of Sevilla

# **LOCAL ORGANIZATION**

# Isbilya Travel

Avda. Américo Vespucio s/n

Isla de la Cartuja 41092 Sevilla, Spain

Phone: +34 95 499 10 68 Fax: +34-954990193

isbilya@nervionviajes.com

### **Local Secretariat**

Mrs. Susana Pazo, susanapazo@esscirc2010.org

### **CONFERENCE SECRETARIAT**

# Instituto de Microelectrónica de Sevilla IMSE-CNM-CSIC

INSE-CIAINI-CSIC

Avda. Américo Vespucio s/n Isla de la Cartuja

41092 Sevilla, Spain

Phone: +34 95 446 66 66 Fax: +34-954466669

info@esscirc2010.org

# **COMMITTEES**

# **STEERING COMMITTEE**

William Redman-White (Chair) NXP

Sorin Cristoloveanu (Vice Chair) ENSERG-IMEP

Cor Claeys (Permanent Secretary) IMEC

Stephen Hall University of Liverpool

Thomas Skotnicki STMicroelectronics

Ralf Brederlow Texas Instruments

Franz Dielacher Infineon

Christian Enz CSEM

Hannu Tenhunen KTH Stockholm

Roberto Bez Numonyx

Roland Thewes TU Berlin

Gaudenzio Meneghesso University of Padova

Doris Schmitt-Landsiedel Technical University Munich

Klaas Bult Broadcom Corporation

Athanasios Dimoulas NCSR DEMOKRITOS

Kazunari Ishimaru

Toshiba America Elect.

Comp.

# **ESSDERC TECHNICAL PROGRAMME COMMITTEE**

Mervin Armstrong QUBelfast

Asen Asenov U.Glasgow

Peter Ashburn Southampton

Emmanuel Augendre CEA-LETI

Giorgio Baccarani U.Bologna

Livio Baldi Numonyx

Anton Bauer Fraunhofer

Romuald Beck TU-Warsaw

Stefan Bengtsson Chalmers

Roberto Bez Numonyx

Josef Boeck Infineon

Mizuno Bunji UJT Lab.

# **COMMITTEES**

# **ESSDERC TECHNICAL PROGRAMME COMMITTEE**

Joachim Burghartz **IMS**

Eugenio Cantatore TU/e

Jean-Pierre Colinge Tyndall

Nadine Collaert IMEC

Univ. Lille Gilles Dambrine

Suman Penn.State Univ. Datta

An De Keersgieter **IMEC**

Kristin De Meyer **IMEC**

Barbara De Salvo CEA-LETI

Stefan Decoutere **IMEC**

Simon Deleonibus CFA-LFTI

Denison Marie Texas Instruments

Charalambos Dimitriadis **AUTH**

Thanasis Dimoulas Demokritos

Akis Doganis **TSMC**

Kelvin **TSMC** Doong

Olof

David

Jaume

Emmanuel Univ. Lille **Dubois**

Engström

CEA-LETI Thomas Ernst

Esseni

Esteve

Univ. Western Australia Lorenzo Faraone

Chalmers

Univ. Udine

**CNM**

Juergen Faul Qimonda

Massimo Fischetti Univ. Massachussets

Flandre UCL Denis

Tibor

Steve

Dimitri

# **COMMITTEES**

# **ESSDERC TECHNICAL PROGRAMME COMMITTEE**

TU-Wien

Gamble Harold QUB

Francisco Gámiz U.Granada

Gérard Ghibaudo **IMFP**

Andrés Godoy U.Granada

Grasser Carlotta Guiducci **EPFL**

Hall

**U.Liverpool**

Luc Haspeslagh **IMEC**

Paul Heremans IMEC

Mingwhei Hong NTHU

Ray Hueting Univ. Twente

Giuseppe lannaccone Univ. Pisa

Iliadis **UMD** Agis

Ioannou

Adrian Ionescu **EPFL**

Fernanda Irrera Univ. Roma 'La Sapienza'

**GMU**

Ishihara **TUDelft** Ryoichi

Kazunari Ishimaru Toshiba

Hiroshi Iwai Titech

STMicroelectronics Herve Jaouen

Erich Kasper Univ. Sttutgart

Qimonda Franz Kreupl

Univ. Stanford Tejas Krishnamohan

Andrea Lacaita Politecnico Milano

LeCarval **CEA-LETI** Gilles

# **COMMITTEES**

# **ESSDERC TECHNICAL PROGRAMME COMMITTEE**

Sung-Young Lee Samsung

Max I emme Univ. Harvard

Ran Liu Fudan Univ.

Salvatore Lombardo **CNR**

Fraunhofer Jürgen Lorenz

Lidia Lukasiak TU-Warsaw

Massimo Macucci Univ. Pisa

Meishoku Masahara **AIST**

Carlos Mazure SOITEC

Bernd Meinerzhagen NST

Gaudenzio Meneghesso Univ. of Padua

Robert Mertens IMEC

Monfray STMicroelectronics Stephane

Victor Moroz Synopsys

Torsen Muller Qimonda

Monserrat Nafría **UABarcelona**

Androula Nassiopoulou **Demokritos**

ISP-Kiev

Nazarov

Alexei

Bich-Yen SOITEC Nguyen

Normand Demokritos Pascal

Masato Kobe University Ogawa

Phil Oldiges **IBM**

Anthony O'Neill Univ. Newcastle

Mikael Östling KTH

Tomás **Palacios** MIT

# **COMMITTEES**

# **ESSDERC TECHNICAL PROGRAMME COMMITTEE**

Davide Pandini STMicroelectronics

Lourdes Pelaz Univ. Valladolid

Henryk Przewlocki TU-Warsaw

Stephan Roche CEA

Noel Rodríguez Univ. Granada

Massimo Rudan Univ. Bologna

Enrico Sangiorgi Univ. Bologna

Andreas Schenk ETHZurich

Jurriaan Schmitz Univ. Twente

Wim Schoenmaker Magwel

Luca Selmi Univ. Udine

Herbert Shea EPF Lausanne

Thomas Skotnicki STMicroelectronics

Ralph Steiner-Vanha Analog

Tetsuya Suemitsu Tohoku Univ.

Yanning Sun IBM

Richard Syms Imperial Colleage

Joseph Tringe Lawrence Livermore Nat. Lab.

Dimitris Tsoukalas NTUA

Ken Uchida Tokyo Institute Tech.

Gerhard Wachutka TU-Munich

Anthony Walton Edinburgh U.

Andreas Wild Freescale

Reinout Woltjer NXP

Jason Woo UCLA

# **ESSDERC TECHNICAL PROGRAMME COMMITTEE**

Dongping Fudan Wu

Kitakyushu Found. Katsunobu Yoshimura

Sandayuki Toshiba Yoshitomi

# **CONFERENCE VENUE**

# **CONFERENCE OVERVIEW**

In addition to contributed papers and plenary lectures, the event will include tutorials, exhibits and satellite workshops to be organized before and after the conference.

An attractive social program will complement the event, featuring a welcome reception, a gala dinner with awards ceremony, and excursions.

# SCHEDULE AT A GLANCE

# Monday, September 13th, 2010 Tutorials

# TUESDAY, SEPTEMBER 14TH, 2010

Conference Opening Technical Sessions Welcome Reception

# WEDNESDAY, SEPTEMBER 15TH, 2010

Technical Sessions Gala Dinner

# THURSDAY, SEPTEMBER 16TH, 2010

**Technical Sessions**

# FRIDAY, SEPTEMBER 17TH, 2010

Workshops

### THE AIM OF THE CONFERENCE

The aim of the ESSDERC conference is to provide an annual European forum for the presentation and discussion of recent advances in solid-state devices and technologies.

# **GENERAL SCOPE OF THE CONFERENCE**

ESSDERC and its sister conference ESSCIRC, which deals with solid-state circuits, are governed by a single Steering Committee. The increasing level of integration for system-on-chip design made available by advances in silicon technology is stimulating more than ever before the need for deeper interaction among technologists, device experts, and circuit and system designers.

While keeping separate Technical Program Committees, ESSDERC and ESSCIRC will share Plenary Keynote Presentations and Joint Sessions bridging both communities. Attendees registered for either conference are encouraged to attend any of the scheduled parallel sessions.

٠

# **CONFERENCE OVERVIEW**

# THEMES OF THE CONFERENCE

The main themes for original contributions to be submitted to ESSDERC 2010 include, but are not limited to the following:

# **ADVANCED CMOS DEVICES**

Ultimate CMOS scaling, high performance, low power and low voltage devices, novel MOS device architectures, high-mobility channel engineered devices, SOI, SGOI, and SiON devices; SiGe, Ge, and strained devices. 3D integrated circuits.

# **PROCESS & INTEGRATION**

Front-end and back-end processes for fabrication of logic memory and 3D integrated circuits; advances in integration for ULSI; advanced/novel memory process integration; logic and mixed-mode IC manufacturing; RF integration; photonics integration.

### **TELECOMMUNICATION**

RF CMOS, analog and mixed signal devices, passives, antennas, filters, RF MEMS, Bipolar, BiCMOS, compound semiconductors and alloys; optoelectronic devices; integrated RF components: inductors, capacitors, and switches.

# **POWER DEVICES**

Smart power devices, high-voltage, high power devices, high temperature operation, SiC devices, CMOS compatible power devices, IC cooling. Discrete and integrated high power/current/voltage devices.

# MODELING AND SIMULATION

Numerical, analytical and statistical modeling of solid-state electronic and optoelectronic devices; compact circuit modeling for devices and interconnects, simulation of front-end and back-end fabrication processes, electro-thermal modeling.

# CHARACTERIZATION, RELIABILITY AND YIELD

Characterization techniques, parameter extraction, advanced test structures and methodologies, reliability issues for new materials and devices; reliability of advanced interconnects, ESD, soft errors, noise and mismatch behavior.

# **MEMORIES**

Novel memory cell concepts, embedded and stand-alone memories, DRAM, FeRAM, MRAM, PCRAM, CBRAM, Flash, SONOS, nanocrystal memories, single and few electron memories, 3D IC stacks, organic memories, 3D integration, reliability and modeling.

# CONFERENCE OVERVIEW

# MEMS, DISPLAYS AND SOC

Design, fabrication, modeling, reliability and packaging of all physical sensors and MEMS categories: bio-sensors for chemical, molecular and biological applications, devices and technologies for lab-on-chip, integration of detectors, sensors, and actuators, CCDs and CMOS imagers, optical on chip communication.

# EMERGING NON-CMOS DEVICES AND TECHNOLOGIES

Nanotubes, nanowires and nanoparticles for electronic, optoelectronic and sensor applications. New device characterization techniques and performance evaluation methodologies.

# GAN-ON-SI TECHNOLOGY, A NEW APPROACH FOR ADVANCED DEVICES

Dr. Tomás Palacios, Massachusetts Institute of Technology

Tomás Palacios, Massachusetts Institute of Technology, United States

- J. W. Chung, Massachusetts Institute of Technology, United States

- K. Ryu, Massachusetts Institute of Technology, United States

- B. Lu, Massachusetts Institute of Technology, United States

# Abstract

The Si substrate of GaN-on-Si wafers offers new opportunities to increase the functionality and performance of nitride-based devices. This paper will review three examples of these new devices/systems. First, GaN-on-Si substrates allow the on-chip heterogeneous integration of GaN and Si electronics.

Second, the easy removal of the Si substrate through dry or wet etching gives access to the N-face of the GaN layer, and all the new device structures that this orientation enables. Finally, the use of Si substrates for the growth of GaN high voltage switches makes the cost of these devices competitive with Si devices, and the total or partial etch of Si brings a new degree of freedom to increase the breakdown and performance of GaN transistors.

Dr. Tomás Palacios is an Associate Professor in the Department of Electrical Engineering and Computer Science at the Massachusetts Institute of Technology, where he leads the Advanced Semiconductor Materials and Devices Group. He received his Ph.D. in Electrical Engineering from the University of California - Santa Barbara, and a M.Sc. degree from the Polytechnical University of Madrid, Spain. His research focuses on the development of new electronic devices to advance the fields of information technology, energy conversion and biosensors. He is especially interested in expanding the frequency performance of GaN transistors and developing new devices and circuits based on graphene. His work has been recognized with multiple awards including, the 2010 Young Scientist Award of the International Symposium on Compound Semiconductors (ISCS), the 2009 NSF CAREER Award, the 2009 ONR Young Investigator Award, the 2008 DARPA Young Faculty Award, the 2006 UCSB Lancaster Award, the Young Researcher Award at the 6th International Conference on Nitride Semiconductors, the European Prize

Salva i Campillo, and several best papers awards. Prof. Palacios has authored more than 100 contributions on advanced semiconductor devices in international journals and conferences, 35 of them invited, 3 book chapters and 8 patents.

# HIGH POWER LEDS FOR SOLID STATE LIGHTING

Dr. Berthold Hahn, OSRAM

### Abstract

For solid stated lighting high light output in combination with high conversion efficacy is essential. High efficiencies are relatively easy to realize at low current densities, but efficiency tends to decline as the current is cranked up. In order to overcome the barriers for high flux LEDs, both epitaxy and chip design have to be optimized.

In this paper we report on the improvement of ThinGaN®-PowerLED structures in epitaxy, chip design, phosphor efficiency and package design. A key for improving LED performance is understanding the carrier loss mechanisms in blue and green epitaxy structures. Assuming an indirect Auger effect as one of the major loss mechanisms in InGaN LEDs, a reduction of the carrier density per emitting well is enabling efficiency improvement for blue/green LEDs.

Along with improved epi designs the extraction efficiency had to be improved. A new chip design allows high current operation in combination with efficiencies beyond 100lm/W for white. New conversion schemes allow the fabrication of extremely efficient green light sources, which enable new generations of high flux projection applications.

**Dr. Berthold Hahn** received his PhD in physics from Regensburg University at 1998.

Dr. Hahn is responsible for chip R&D at OSRAM Opto Semiconductors for visible and infrared LEDs. He joined OSRAM Opto Semiconductors in 1998. He was responsible for the epi development of InGaN-based LEDs. He headed the Thin-GaN programand took over responsibility for nitride-based high-power chip development. Since 2008 he has also been responsible for R&D of AllnGaP- and AlGaAs-based LEDs.

TRENDS AND PERSPECTIVES FOR ELECTRICAL CHARACTERIZATION AND RELIABILITY ASSESSMENT IN ADVANCED CMOS DEVICES AND TECHNOLOGIES

Dr. Guido Groeseneken, IMEC

Guido Groeseneken, IMEC, Belgium Robin Degraeve, IMEC, Belgium Ben Kaczer, IMEC, Belgium Koen Martens, IMEC, Belgium

## Abstract

In this paper we give a brief historical review of the evolution of device reliability research over the past decades.

Then we give some examples on how established characterization techniques that were developed for silicon based devices can be completely misinterpreted when applied to Ge or III-V based MOS-structures, and how a simple modification of the technique can ensure a correct interpretation. We also show how novel techniques, such as TSCIS (Trap spectroscopy by Charge Injection and Sensing), were developed recently to overcome the problem of dielectric material screening for logic and memory applications. With the scaling of the devices into the nanometer regime single traps are causing large variations in the device parameters, which leads to a time-dependent variability, which makes lifetime analysis difficult. Finally we show that when using the classical reliability assessment methodology based on accelerated testing, the available reliability margins are strongly reduced, in some cases even down to zero, especially for sub-1nm EOT (Effective Oxide Thickness) devices. As a result, we argue that the reliability community will have to look for alternative ways to ensure and guarantee the lifetime of future products.

**Dr. Guido Groeseneken** received the M.Sc. degree in electrical engineering (1980) and the Ph.D degree in applied sciences (1986), both from the Katholieke Universiteit Leuven, Belgium. In 1987 he joined the R&D Laboratory of IMEC (Interuniversity Microelectronics Center) in Leuven, Belgium, where he is responsible for research in reliability physics for deep submicron CMOS technologies. From October 2005 until April 2007 he was also responsible for the IMEC Post CMOS Nanotechnology program within IMEC's core partner research program. Since 2001 he is Professor at the KU Leuven, where he is Program Director of the Master in Nanoscience and Nanotechnology, and where he is also

coordinating a European Erasmus Mundus Master program in Nanoscience and nanotechnology. He became an IEEE Fellow in 2005 and an IMEC Fellow in 2007.

He has made contributions to the fields of non-volatile semi-conductor memory devices and technology, reliability physics of VLSI-technology, hot carrier effects in MOSFET's, time-dependent dielectric breakdown of oxides, Negative-Bias-Temperature Instability effects, ESD-protection and -testing, plasma processing induced damage, electrical characterization of semiconductors and characterization and reliability of high k dielectrics. Recently he has also interest in nanotechnology for post-CMOS applications, such as carbon nanotubes for interconnect applications, tunnel FET's for alternative nanowire devices etc.

He has served as a technical program committee member of several international scientific conferences, among which the IEEE International Electron Device Meeting (IEDM), the European Solid State Device Research Conference (ESS-DERC), the International Reliability Physics Symposium (IRPS), the IEEE Semiconductor Interface Specialists Conference (SISC) and the EOS/ESD Symposium. From 2000 until 2002 he also acted as European Arrangements Chair of IEDM. In 2005 he was the General Chair of the Insulating Films on Semiconductor (INFOS) conference, organized in Leuven, Belgium.

He has authored or co-authored more than 500 publications in international scientific journals and in international conference proceedings, 6 book chapters and 10 patents in his fields of expertise.

# **ESSDERC TUTORIALS**

# SSDERC TUTORIALS

MONDAY, SEPTEMBER 13TH, 2010

TUTORIAL 1: NANOELECTRONICS: A TOOL TO FACE THE FUTURE.

Organisers: Francisco Gámiz and Andrés Godoy, *University of Granada*

Full-Day Tutorial (8:50 - 17:20)

# Room D

### Content

The aim of this Tutorial is to present the status and trends of different hot topics in the field of nanoelectronics. All the presentations will consist on a 50 minutes oral presentation + 10 minutes of questions.

# Agenda

8:50-9:00

Introduction

F. Gámiz, A. Godoy, University of Granada

9:00-10:00

CMOS process variability – from technology to circuits and systems

J. Lorenz, Fraunhofer Institute, Germany

10:00-11:00

Industrial challenges for the CMOS technology to reach the 22nm and 16nm nodes

T. Skotnicki, STMicroelectronics, France

11:00-11:20 BREAK

11:20-12:20

1T-DRAM structures

Sorin Cristoloveanu, IMEP-LAHC, France

12:20-14:00 LUNCH

14:00-15:00

III-V devices for high frequency applications

Tomás Palacios, MIT

15:00-16:00

Silicon nanowires

T. Ernst, CEA-LETI, Grenoble, France

16:00-16:20 BREAK

16:20-17:20

Carbon based Nanoelectronics: Carbon Nanotubes & Graphene as drivers to device innovation and Post-CMOS area

Sthephan Roche, CEA, INAC, SP2M, Grenoble, France

# **ESSDERC TUTORIALS**

# TUTORIAL 2: SILICON ON INSULATOR: MATERIALS TO CIRCUIT DESIGN.

Organiser: Jean-Pierre Colinge, Tyndall Institute, Cork Ire-

Full-Day Tutorial (9:00 - 17:00)

### Room E

### Content

This tutorial will cover different aspects of SOI technology, ranging form substrate preparation to circuit design. The Smart-Cut® technique has enabled the mass production of SOI wafers, but is also a powerful technique for the formation of hybrid substrates and for More the Moore applications. The particular properties of SOI MOSFETs can be used to improve circuit speed or electrical performance. These properties will be reviewed and compact models for SOI MOSFETs will be presented. Design techniques and tools for analogue, digital and RF applications will be described.

# Agenda 9:00-10:00

9:00-T0:00

Smart-cut enabled materials

C Colinge, Tyndall

10:00-11:00

Physics of SOI devices

JP Colinge, Tyndall

11:00-12:00

SOI MOSFET compact models

B Iniguez, URV

12:00-14:00 LUNCH

14:00-15:00

SOI Design: RF

JP Raskin, UCL

15:00-16:00

SOI design: analog

D Flandre, UCL

16:00-17:00

SOI design: logic circuits

Ph Flatresse, STM

For further information about these tutorials, please visit the webpage of the conference at http://www.essderc2010.org/essdercTut.html

# **TUESDAY SEPTEMBER 14**

Process Integration: More than Moore Devices Architectures

(Lecture)

Session Code: A3L-B

Location: Room B

Date & Time: Tuesday September 14, 2010

(11:20 - 13:00)

Chair(s): Francis Balestra

IMEP-LAHC Laboratory, France

Anton Bauer

IISB-Fraunhofer, Germany

# 11:20 Silicon Photodiodes for High-Efficiency Low-Energy Electron Detection

Agata Sakic, Lis Nanver, Tom Scholtes, Carel Heerkens, TU *Delft*. Gerard van Veen, Kees Kooijman, Patrick Vogelsang, *FEI company*.

# 11:40 New Mechanism of Plasma Induced Damage on CMOS Image Sensor: Analysis and Process Optimization

Jean-Pierre Carrere, Jean-Pierre Oddou, Claire Richard, Cecile Jenny, Maxime Gatefait, Sebastien Place, Christophe Aumont, Arnaud Tournier, Francois Roy, *STMicroelectronics*.

# 12:00 Drain-Extended MOS Transistors Capable for Operation at 10V and at Radio Frequencies Andreas Mai, Holger Rücker, *IHP Innovations for High Performance Microelectronics*.

# 12:20 Analysis of Silicon on-Chip Integrated Antennas for Intra- and Inter-Chip Wireless Interconnects T. Kikkawa, K. Kimoto S. Kubota, Hiroshima University.

# 12:40 Passive Components Integration in CMOS Technology

Siamak Salimy, Fatiha Challali, Antoine Goullet, Marie-Paule Besland, Serge Toutain, Dominique Averty, Ahmed Rhallabi, Jean-Pierre Landesman, Nantes University. Jean-Claude Saubat, Alain Charpentier, MHS Electronics.

# **TUESDAY SEPTEMBER 14**

# Reliability, variability and mismatch

(Lecture)

Session Code: A3L-C

Location: Room E

Date & Time: Tuesday September 14, 2010

(11:20 - 13:00)

Chair(s): Montserrat Nafría,

UAB Universitat Autònoma de Barce-

Iona, Spain Reinout Woltjer, NXP, Netherlands

# 11:20 Drain Current Variability in 45nm Heavily Pocket-Implanted Bulk MOSFET

Cecilia Mezzomo, STMicroelectronics, IMEP-LAHC. Aurelie Bajolet, STMicroelectronics. Augustin Cathignol, IBM France. Gerard Ghibaudo, IMEP-LAHC.

### 11:40 Mismatch Sources in LDMOS Devices

sity of Glasgow.

Pietro Andricciola, Hans Tuinhout, NXP Semiconductors.

12:00 Combining Process and Statistical Variability in the Evaluation of the Effectiveness of Corners in Digital Circuit Parametric Yield Analysis Plamen Asenov, Noor Ain Kamsani, David Reid, Campbell Millar, Scott Roy, Asen Asenov, Univer-

12:20 Threshold Voltage Shift and Drain Current Degradation by NBT Stress in Si (110) pMOSFETs

Kensuke Ota, Masumi Saitoh, Yukio Nakabayashi,

Takamitsu Ishihara, Toshinori Numata, Toshiba Corporation. Ken Uchida, Tokyo Institute of Technology.

# 12:40 Resistive Switching-Like Behaviour of the Dielectric Breakdown in Ultra-Thin Hf Based Gate Stacks in MOSFETs

Albert Crespo-Yepes, Javier Martín-Martínez, *Universitat Autònoma de Barcelona*. Aude Rothschild, *IMEC*. Rosana Rodríguez, Montse Nafría, Xavier Aymerich, *Universitat Autònoma de Barcelona*.

# **TUESDAY SEPTEMBER 14**

# SRAM and DRAM

(Lecture)

Session Code: A3L-D

Location: Room D

Date & Time: Tuesday September 14, 2010

(11:20 - 13:00)

Chair(s): Barbara De Salvo,

CEA-LETI, France Andreas Schenk,

ETH Zurich, Switzerland

# 11:20 Tri-Gate Bulk CMOS Technology for Improved SRAM Scalability

Changhwan Shin, *University of California*, *Berkeley*. Chen Hua Tsai, Mei Hsuan Wu, Chung Fu Chang, You Ren Liu, Chih Yang Kao, Guan Shyan Lin, Kai Ling Chiu, Chuan-Shian Fu, Cheng-Tzung Tsai, Chia Wen Liang, *United Microelectronics Corporation*. Borivoje Nikolic, Tsu-Jae King Liu, *University of California*, *Berkeley*.

# 11:40 Impact of Fast-Recovering NBTI Degradation on Stability of Large-Scale SRAM Arrays

Stefan Drapatz, *TU München*. Karl Hofmann, Georg Georgakos, *Infineon Munich*. Doris Schmitt-Landsiedel, *TU München*.

# 12:00 Experimental Comparison of Programming Mechanisms in 1T-DRAM Cells with Variable Channel Length

Alexandre Hubert, CEA Leti Minatec. Maryline Bawedin, IMEP, INPG-Minatec. Georges Guegan, CEA Leti Minatec. Sorin Cristoloveanu, IMEP, INPG-Minatec. Thomas Ernst, CEA Leti Minatec. Olivier Faynot, CEA Leti Minatec.

# 12:20 Substrate Bias Dependency of Sense Margin and Retention in Bulk FinFET 1T-DRAM Cells

Nadine Collaert, Marc Aoulaiche, An De Keersgieter, Bart De Wachter, Malgorzata Jurczak, Laith Altimime. *IMEC*.

# 12:40 COLK cell: A new embedded DRAM architecture for advanced CMOS nodes

Sébastien Cremer, Olivier Goducheau, Hervé Petiton, Sébastien Gaillard, Emek Yesilada, Marc Vernet, Cécile Jenny, Frédéric Lalanne, STMicroelectronics.

# **TUESDAY SEPTEMBER 14**

# Alternative FETs

(Lecture)

Session Code: A4L-B

Location: Room B

Date & Time: Tuesday September 14, 2010

(14:50 - 15:50)

Chair(s): Nadine Collaert,

IMEC, Belgium Thanasis Dimoulas, Demokritos, Greece

# 14:50 Sub-60nm Si Tunnel Field Effect Transistors with $I_{on} > 100 \mu A/ \mu m$

Wei Yip Loh, SEMATECH. Kanghoon Jeon, SEMATECH/University of California Berkeley. Chang Yong Kang, Jungwoo Oh, SEMATECH. Pratik Patel, University of California Berkeley. Casey Smith, Joel Barnett, Chanro Park, SEMATECH. Tsu-Jae King Liu, University of California Berkeley. Hsing-Huang Tseng, Texas State University.Prashant Majhi, SEMATECH Intel. Raj Jammy, SEMATECH. Chenming Hu, University of California Berkeley.

15:10 High-Performance Enhancement-Mode In<sub>0.53</sub>Ga<sub>0.47</sub>As Surface Channels n-MOSFET with Thin In<sub>0.2</sub>Ga<sub>0.8</sub>As capping and Laser anneal effect

Injo Ok, Pui-Yee Hung, Dmitry Veksler, Jungwoo Oh, Prashant Majhi, Raj Jammy, *SEMATECH*.

15:30 Optimization of Tunnel FETs: Impact of Gate Oxide Thickness, Implantation and Annealing Conditions

Daniele Leonelli, *IMEC /KU Leuven*. Anne Vandooren, Rita Rooyackers, *IMEC*. Stefan De Gendt, Marc Heyns, Guido Groeseneken, *IMEC/KU Leu-*

ven.

# **TUESDAY SEPTEMBER 14**

# Special characterization methods and structures (Lecture)

Session Code: A4L-C

Location: Room E

Date & Time: Tuesday September 14, 2010

(14:50 - 15:50)

Chair(s): Sorin Cristoloveanu,

IMEP-LAHC, France

- 14:50 Test Structure and Method for the Experimental Investigation of Internal Voltage Amplification and Surface Potential of Ferroelectric MOSFETs Alexandru Rusu, Giovanni Salvatore, Adrian Ionescu, EPFL Ecole Polytechnique Federale de Lausanne.

- 15:10 Experimental Evidence of Unconventional Room-Temperature Quantum Hall Effect (RTQHE) in 65nm Si nMOSFETs at Very Low Magnetic Fields

Edmundo Gutiérrez-D., *INAOE*. Fernando Guarin, *IBM Microelectronics*.

15:30 Thermal Broadening of Two-Dimensional Electron Gas Mobility Distribution in AlGaN/AIN/GaN Heterostructures

Gilberto A. Umana-Membreno, *The University of Western Australia*. Tiziana Stomeo, Vittorianna Tasco, Adriana Passaseo, Massimo De Vittorio, *CNR-NANOSCIENZE*. Lorenzo Faraone, *The University of Western Australia*.

# **ESSDERC PROGRAMME**

# **TUESDAY SEPTEMBER 14**

# Advances in algorithms and simulation methods

(Lecture)

Session Code: A4L-D

Location: Room D

Date & Time: Tuesday September 14, 2010

(14:50 - 15:50)

Chair(s): Jürgen Lorenz,

IISB-Fraunhofer, Germany

### 14:50 Hardware/Software Co-Simulation for the Rapid Prototyping of an Acceleration Sensor System with Force-Feedback Control

Ruslan Khalilyulin, Thomas Steinhuber, Gabriele Schrag, Gerhard Wachutka, TU München.

### 15:10 On the Inclusion of Lorentz Force Effects in TCAD Simulations

Wim Schoenmaker, Peter Meuris, MAGWEL NV. Jean Jimenez, Philippe Galy, STMicroelectronics.

### 15:30 Modeling Methodology of High-Voltage Substrate Minority and Majority Carrier Injections

Fabrizio Lo Conte, Jean-Michel Sallese, Maher Kayal, EPFL Ecole Polytechnique Federale de Lausanne.

# **TUESDAY SEPTEMBER 14**

### SOI MOSFETs

(Lecture)

Session Code: A6I -B

Location: Room B

Date & Time: Tuesday September 14, 2010

(17:20 - 18:40)

Chair(s): Kazunari Ishimaru,

> Toshiba, Japan Carlos Mazuré, SOITEC, France

# 17:20 Subthreshold FinFET SRAM Cell Optimization Considering Surface-Orientation Dependent Variability

Ming-Long Fan, Vita Pi-Ho Hu, Chien-Yu Hsieh, Pin Su, Ching-Te Chuang, *National Chiao Tung University*.

# 17:40 Fin-Height Controlled PVD-TiN Gate FinFET SRAM for Enhancing Noise Margin

Yongxun Liu, K. Endo, Shin-Ichi O'Uchi, Junichi Tsukada, Hiromi Yamauchi, Yuki Ishikawa, Kunihiro Sakamoto, Takashi Matsukawa, Meishoku Masahara, *Nanoelectronics Research Institute of AIST*. T. Kamei, T. Hayashida, A. Ogura, *Meiji University.*

# 18:00 Dual Channel and Strain for CMOS Co-Integration in FDSOI Device Architecture

Cyrille Le Royer, Mikaël Cassé, François Andrieu, Olivier Weber, Laurent Brevard, Pierre Perreau, Jean-François Damlencourt, Sophie Baudot, Claude Tabone, Fabienne Allain, Pascal Scheiblin, Caroline Rauer, Louis Hutin, *CEA Leti Minatec.* C. Figuet, C. Aulnette, N. Daval, B.-Y. Nguyen and K. K. Bourdelle, *SOITEC.*

# 18:20 UT2B-FDSOI Device Architecture Dedicated to Low Power Design Techniques

Jean-Philippe Noel, Olivier Thomas, Marie-Anne Jaud, CEA-Leti. Claire Fenouillet-Beranger, CEA-Leti/STMicroelectronics. Pierrette Rivallin, Pascal Scheiblin, Thierry Poiroux, CEA-Leti. Frédéric Boeuf, STMicroelectronics. François Andrieu, Olivier Weber, Olivier Faynot, CEA-Leti. Amara Amara, ISEP.

#### **TUESDAY SEPTEMBER 14**

## Ferromagnetic and polycrystalline devices

(Lecture)

Session Code: A6L-C

Location: Room E

Date & Time: Tuesday September 14, 2010

(17:20 - 18:40)

Steve Hall. Chair(s):

University of Liverpool, UK

Ryoichi Ishihara, TU Delft. Netherlands

#### 17:20 **Ultra-low Volume Ferromagnetic Nanodots for Field-coupled Computing Devices**

Josef Kiermaier, Stephan Breitkreutz, Xueming Ju, TU München. Gyorgy Csaba, University of Notre Dame. Doris Schmitt-Landsiedel, Markus Becherer, TH München

#### 17:40 The Curie Temperature As a Key Design Parameter of Ferroelectric Field Effect Transistors

Giovanni Antonio Salvatore, Livio Lattanzio, Didier Bouvet, Adrian M. Ionescu, EPFL Ecole Polytechnique Federale de Lausanne.

#### 18:00 Performance Trade-Offs in Polysilicon Source-**Gated Transistors**

Radu Sporea, University of Surrey. Mike Trainor, Nigel Young, Philips Research. John Shannon, Ravi Silva, University of Surrey.

#### 18:20 Analysis and Modeling of Pseudo-Short-Channel Effects in ZnO-Nanoparticle Thin-Film Transistors

Karsten Wolff, Ulrich Hilleringmann, University of Paderborn.

#### WEDNESDAY SEPTEMBER 15

#### Simulation of advanced silicon devices

(Lecture)

Session Code: B3L-B

Location: Room B

Date & Time: Wednesday September 15, 2010

(11:20 - 13:00)

Chair(s): Bernd Meinerzhagen,

Technical University of Braunschweig,

Germany

Massimo Rudan.

University of Bologna, Italy

#### 11:20 Comparison of Strained SiGe Heterostructureon-Insulator (001) and (110) PMOSFETs: C-V Characteristics, Mobility and ON Current

Anh-Tuan Pham, Technical University of Braunschweig. Christoph Jungemann, Bundeswehr University in Munich. Bernd Meinerzhagen, Technical University of Braunschweig.

#### A New Model for the Backscatter Coefficient in 11:40 Nanoscale MOSFETs

Jan-Laurens van der Steen, University of Twente. Pierpaolo Palestri, David Esseni, University of Udine. Ray Hueting, University of Twente.

#### 12:00 Multi-Subband Monte Carlo Simulation of Bulk MOSFETs for the 32nm-Node and Beyond

Carlos Sampedro, Francisco Gámiz, Andrés Godov, University of Granada, Raúl Valín, Antonio García-Loureiro, University of Santiago de Compostela. Noel Rodríguez, University of Granada.

#### Modeling Study on Carrier Mobility in Ultra-Thin 12:20 **Body FinFETs with Circuit-Level Implications**

Mirko Poljak, University of Zagreb. Vladimir Jovanovic, TU Delft/University of Zagreb. Tomislav Suligoi. University of Zagreb.

#### 12:40 TCAD Based Device Architecture Exploration Towards Half-Terahertz Silicon/Germanium Heterojunction Bipolar Technology

Arturo Sibaja-Hernández, Shuzhen You, Stefaan Van Huylenbroeck, Rafael Venegas, Kristin De Meyer, Stefaan Decoutere, *IMEC*.

#### WEDNESDAY SEPTEMBER 15

#### **Photodetectors**

(Lecture)

Session Code: B3L-C

Location: Room E

Date & Time: Wednesday September 15, 2010

(11:20 - 13:00)

Chair(s): Anthony O'Neill,

New Castle University, UK

Mervin Armstrong,

Queen's University Belfast, UK

## 11:20 Integrated Phototransistors in a CMOS Process for Optoelectronic Integrated Circuits

Plamen Kostov, Wolfgang Gaberl, Horst Zimmermann, Vienna University of Technology.

#### 11:40 CMOS Process Enhancement for High Precision Narrow Linewidth Applications

Frank Hochschulz, Uwe Paschen, Holger Vogt, Fraunhofer IMS.

# 12:00 A 2µm Diameter, 9Hz Dark Count, Single Photon Avalanche Diode in 130nm CMOS Technology Justin Richardson, Lindsay Grant, STMicroelec-

tronics. Eric Webster, Robert Henderson, *University* of *Edinburgh*.

#### 12:20 Buried Finger Concept for a Correlating Double Cathode Photodetector in BiCMOS

Alexander Nemecek, University of Applied Sciences Wr. Neustad/t/Vienna University of Technology. Horst Zimmermann, Vienna University of Technology.

# 12:40 Understanding Dark Current in Pixels of Silicon Photomultipliers

Roberto Pagano, Salvatore Lombardo, Sebania Libertino, *CNR*. Giuseppina Valvo, Giovanni Condorelli, Beatrice Carbone, Delfo Nunzio Sanfilippo, Piero Giorgio Fallica. *ST Microelectronics*.

#### **WEDNESDAY SEPTEMBER 15**

# Silicon and Gallium Nitride power devices (Lecture)

Session Code: B3L-D

Location: Room D

Date & Time: Wednesday September 15, 2010

(11:20 - 13:00)

Chair(s): Marie Denison,

Texas Instruments, USA Gerhard Wachutka, TU München, Germany

# 11:20 Hot-Carrier Stress Induced Degradation in Multi-STI-Finger LDMOS: an Experimental and Numerical Insight

Stefano Poli, Alberto Loi, Susanna Reggiani, Giorgio Baccarani, Elena Gnani, Antonio Gnudi, *University of Bologna*. Marie Denison, Sameer Pendharkar, Rick Wise, Sridhar Seetharaman, *Texas Instruments*.

## 11:40 Repetitive Avalanche Cycling of Low-Voltage Power Trench N-MOSFETs

Olayiwola Alatise, Ian Kennedy, George Petkos, Keith Heppenstall, Khalid Khan, Adrian Koh, Phil Rutter, *NXP Semiconductors*.

12:00 Investigation of a Dual Channel N/P-LDMOS and Application to LDO Linear Voltage Regulation Marie Denison, Yizhong Xie, Hannes Estl, Texas Instruments.

#### 12:20 High Transconductance A1GaN/GaN HEMT with Thin Barrier on Si(111) Substrate

Francois Lecourt, Douvry Yannick, Nicolas Defrance, Virginie Hoel, Jean-Claude De Jaeger, *IEMN*. Samira Bouzid, M. Renvoise, Derek Smith, Hassan Maher, *OMMIC*.

#### 12:40 Study of GaN HEMTs Electrical Degradation by Means of Numerical Simulations

Valerio Di Lecce, Michele Esposto, Matteo Bonaiuti, Fausto Fantini, Alessandro Chini, *Universitá di Modena e Reggio Emilia*.

#### WEDNESDAY SEPTEMBER 15

# **Modeling of temperature and stress impacts** (Lecture)