# **WELCOME TO ESSCIRC 2010**

On behalf of the Organizing Committees of ESSCIRC 2010, it is our pleasure to welcome you to the 36th European Solid-State Circuits Conference. ESSCIRC 2010 runs parallel to his sister conference ESSDERC 2010, covering all aspects of modern solid-state systems, circuits and devices at a single event. In combination, these two conferences provide a unique forum where technologists, device experts, and circuit and system designers can interact. This interaction is instrumental to fully exploiting the potential of modern devices and technologies when confronting the challenges of system-on-chip (SoC) integration. As a delegate at 👝 ESSCIRC-ESSDERC 2010 you will have the opportunity to learn of the latest advances in these fields, and to meet those who have dared, pioneered, and succeeded.

The conferences are to be held at the Barceló Hotel Renacimiento, on the Isla de la Cartuja, an island located between two branches of the Guadalquivir river which today is home to the Cartuja 93 technology business park. Seville's downtown (El Centro) is very close by and, from there, visitors will find Seville's major monuments and shops just a few short steps away.

This year, a total of 265 submissions from 34 different countries were received for ESSCIRC including 148 papers from Europe, 70 from Asia-Pacific, 32 from North and South America and 15 from the Middle East and Africa. This is proof of the truly international nature of ESSCIRC. The Technical Program Committee with about 110 world-class experts from academia and industry selected 114 papers for oral presentation. Twelve plenary presentations by guest speakers complete the program by focusing on highly topics selected by the Technical Program relevant Committees of both conferences. In addition to the conference programs, a pre-conference day with introductory tutorials and a post-conference day with workshops showcasing work currently being carried out by European research consortia will also be held.

We would like to thank the Steering Committee of ESSCIRC-ESSDERC for giving us the opportunity to organize this event. The meeting has been organized by members of the Institute of Microelectronics of Seville (CNM-CSIC), the University of Seville and the University of Granada. We would like to thank

### **WELCOME TO ESSCIRC 2010**

the authorities of these institutions for allowing us to devote part of our time to the organization.

We have been extremely fortunate to have the help of an outstanding team of volunteers of the Organizing Committee and the Technical Program Committee, who have all worked very hard. We are hugely indebted to all these volunteers. Our warm thanks to all of them for their dedication, enthusiasm and professionalism.

Last but not least, we would like also to express our greatest appreciation to all the authors who submitted papers to the conference and to all delegates, tutorial lecturers and plenary speakers who have travelled to Seville to interact and share their thoughts during the Conference. They will play a leading role at the event.

Enjoy ESSCIRC-ESSDERC 2010 and your visit to Seville. We hope to see you all back here more often!

Welcome / Bienvenidos !!

José L. Huertas Ángel Rodríguez-Vázquez General Chairs - ESSCIRC-ESSDERC 2010

# **ABOUT IMSE/US**

The "Instituto de Microelectrónica de Sevilla" (IMSE) is a R&D centre specialized on design and test of analogue, mixed-signal and sensory-processing integrated circuits as well as on their use in any application context, specially in RF, microsystems, data conversion...

IMSE, together with the Microelectronics Institutes in Barcelona (IMB) and Madrid (IMM) form the Spanish National Microelectronics Centre (CNM) operated under the umbrella of "Consejo Superior de Investigaciones Científicas" (CSIC).

The personnel from IMSE has been carrying out research, teaching and technology transfer for more than 20 years. In particular, teaching is done as regular courses offered by the University of Seville and as courses and seminars given elsewhere on demand. The PhD thesis and the research projects within IMSE are mainly focusing on the implementation of innovative concepts in silicon, paying special attention to their experimental verification.

Starting on 2009, IMSE is providing external services based on a tester Agilent 93000, giving training, technical support and test-board design for implementing and debugging test procedures both in analogue and digital.

In addition, IMSE offers an academic master: Master in Microelectronics Design and Applications of Micro/Nanometric Systems. It is oriented to provide professionals with a scientific, technological, and sociol-economic education in Micro - Nano electronics.

On the other hand, the "Universidad de Sevilla" (US) is a topranked European university. Founded under the name of Colegio Santa María de Jesús in 1505, the university of Seville, with a student body of over 55,000, is one of the most important higher education institutions in the country. The Faculties, Technical High Schools, Polytechnics and University Schools are the centres in charge of organizing the teaching as well as the academic, administrative and managerial processes leading to obtaining a degree.

Public service of higher education is assigned to this university and carried out through the study, teaching and research as well as through the generation, development and diffusion of knowledge at society and citizenship's service, offering as well, scientific and technical support for the cultural, social, economic and territorial development and the concern for training professionals.

About University of Granada (please see ESSDERC Programme, pages 3 and 4).

# CONTENTS

CONTENTS

| ESSCIRC Schedule            | 5  |

|-----------------------------|----|

| Meeting Rooms Floorplan     | 7  |

| Programme at a glance       | 8  |

| Committees                  | 11 |

| Welcome to Sevilla          | 18 |

| Conference Venue            | 23 |

| Conference Information      | 29 |

| Conference Overview         | 30 |

| Meals and Refreshments      | 33 |

| Social Programme            | 34 |

| Optional Leisure Activities | 35 |

| Joint Plenary Talks         | 38 |

| ESSCIRC Plenary Talks       | 45 |

| ESSCIRC Tutorials           | 49 |

| ESSCIRC Programme           | 53 |

| ESSCIRC Workshops           | 82 |

| ESSCIRC Fringe              | 86 |

# SCHEDULE

# **ESSCIRC SCHEDULE**

#### Monday, September 13th, 2010

Tutorials Rooms C, D, E, F

#### Tuesday, September 14th, 2010

8:30 Conference Opening

#### Technical Sessions

| 9:00 | Joint Plenary Lecture |

|------|-----------------------|

| 9:50 | Joint Plenary Lecture |

10:40 Coffee Break

11:00 Fringe Poster Briefing Session

11:20 ESSCIRC Sessions

13:00 Lunch

14:20 Fringe Poster Briefing Session 14:50 ESSCIRC Plenary Lecture

15:50 ESSCIRC Sessions

16:50 Coffee Break

17:20 ESSCIRC Sessions

18:40 Fringe Poster Briefing Session

#### **Welcome Reception**

### Wednesday, September 15th, 2010

#### **Technical Sessions**

| 9:00 | Joint Plenary Lecture |

|------|-----------------------|

| 9:50 | Joint Plenary Lecture |

10:40 Coffee Break

11:20 ESSCIRC Sessions

13:00 Lunch

14:50 ESSCIRC Plenary Lecture

15:50 ESSCIRC Sessions

16:50 Coffee Break

17:20 ESSCIRC Sessions

#### **Gala Dinner**

# Thursday, September 16th, 2010

#### **Technical Sessions**

| 9:00 | Joint Plenary Lecture |

|------|-----------------------|

| 9:50 | Joint Plenary Lecture |

10:40 Coffee Break

11:20 ESSCIRC Sessions

# **ESSCIRC SCHEDULE**

SCHEDULE

13:00 Lunch

14:50 ESSCIRC Plenary Lecture

15:50 ESSCIRC Sessions 16:50 Coffee Break

17:20 ESSCIRC Sessions

Friday, September 17th, 2010

Workshops

Rooms C, D, E, F

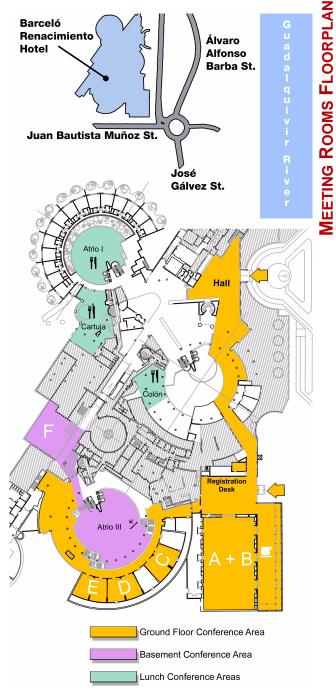

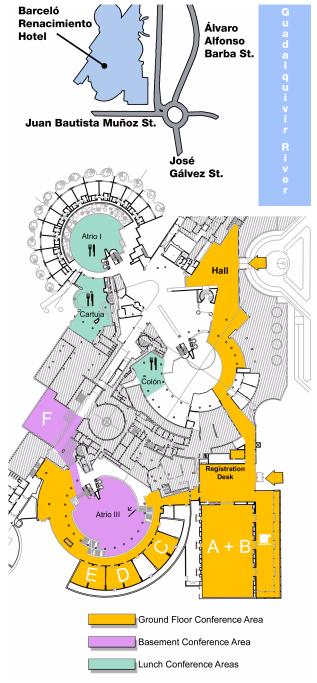

# **MEETING ROOMS FLOORPLAN**

# PROGRAMME AT A GLANCE

# PROGRAMME AT A GLANCE

| 010    |

|--------|

| #<br># |

| oer 17 |

| pteml  |

| ay Se  |

| nesda  |

| =      |

| Incona) oc                           | inceday Schiember 14til, 2010                                                                                  |                                                                                                                                                               |                                                                                                                                                                    |                                                                  |                                                                                                                                          |                                                                                                                                                          |

|--------------------------------------|----------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| Time                                 | ROOM B                                                                                                         | ROOM E                                                                                                                                                        | ROOM D                                                                                                                                                             | ROOM A                                                           | ROOM C                                                                                                                                   | ROOM F                                                                                                                                                   |

| 8:30                                 |                                                                                                                | CONFERENCE OPENIN                                                                                                                                             | CONFERENCE OPENING (Prof. Ángel Rodríguez-Vázquez and Prof. José Luís Huertas) ROOM A+B                                                                            | and Prof. José Luís Huertas)                                     | ROOM A+B                                                                                                                                 |                                                                                                                                                          |

| 09:00-09:20                          |                                                                                                                | JOINT PL                                                                                                                                                      | A1L-A (ROOM A+B) JOINT PLENARY: High Performance Mixed Signal - Business and Technology SPEAKER: Dr. Rene Penning de Vries (NXP)                                   | (+B)<br>ignal - Business and Techn<br>g de Vries (NXP)           | ology                                                                                                                                    |                                                                                                                                                          |

| 09:50-10:40                          |                                                                                                                | JOINT PLEN.                                                                                                                                                   | A2L-A (ROOM A+B) JOINT PLENARY: 3D Integration Technology: Status and Application Development SPEAKER: Dr. Peter Ramm (Fraunhofer IZM Munich Division)             | (+B)<br>tatus and Application Devel<br>ofer IZM Munich Division) | opment                                                                                                                                   |                                                                                                                                                          |

| 10:40-11:00                          |                                                                                                                |                                                                                                                                                               | COFFEE BREAK                                                                                                                                                       |                                                                  |                                                                                                                                          |                                                                                                                                                          |

| 11:00-11:20                          |                                                                                                                |                                                                                                                                                               | FRINGE POSTER BRIEFING SESSION                                                                                                                                     | SESSION                                                          |                                                                                                                                          |                                                                                                                                                          |

| 11:20-13:00 A3L-B<br>Proces<br>Moore | 9 A3L-B A3L-B Process Integration: More than Reliability, variability and Moore Devices Architectures mismatch | A3L-C<br>Reliability, variability and<br>mismatch                                                                                                             | A3L-D<br>SRAM and DRAM                                                                                                                                             | A3L-F<br>Analog Voltage<br>References                            | A3L-G<br>Imagers                                                                                                                         | A3L-H<br>RF Frequency Synthesis                                                                                                                          |

| 13:00-14:20                          |                                                                                                                |                                                                                                                                                               | LUNCH                                                                                                                                                              |                                                                  |                                                                                                                                          |                                                                                                                                                          |

| 14:20-14:50                          |                                                                                                                |                                                                                                                                                               | FRINGE POSTER BRIEFING SESSION                                                                                                                                     | SESSION                                                          |                                                                                                                                          |                                                                                                                                                          |

| 14:50-15:50 A4L-B<br>Altern          | ) A4L-B<br>Alternative FETs                                                                                    | A4L-C<br>Special characterization<br>methods and structures                                                                                                   | A4L-D<br>Advances in algorithms and<br>simulation methods                                                                                                          | ESSCIRC PLENARY: Terah<br>SPEAKER: Dr. Ullr                      | A4L-A (ROOM A) PLENARY: Terahertz Imaging with CMOS/BiCMOS Process Tech SPEAKER: Dr. Ullrich Pfeiffer (University of Wuppertal, Germany) | A4L-A (ROOM A) ESSCIRC PLENARY: Terahertz Imaging with CMOS/BICMOS Process Technologies SPEAKER: Dr. Ullrich Preiffer (University of Wuppertal, Germany) |

| 15:50-16:50                          |                                                                                                                | A5L-A (ROOM B) SDERC PLENARY: Galvon-Si Technology, A New Approach for Advanced Devi SPEAKER: Dr. Tomás Palacios (Massachusetts Institute of Technology, USA) | A5L-4 (ROOM B) ESSDERC PLENARY: GaN-on-Si Technology, A New Approach for Advanced Devices SPEAKER: Dr. Tomás Palacios (Massachusetts Institute of Technology, USA) | A5L-F<br>Amplifiers I                                            | A5L-G<br>Micropower AD<br>interfaces                                                                                                     | A5L-H<br>mm-Wave Transceivers                                                                                                                            |

| 16:50-17:20                          |                                                                                                                |                                                                                                                                                               | COFFEE BREAK                                                                                                                                                       |                                                                  |                                                                                                                                          |                                                                                                                                                          |

| 17:20-18:40 AGL-B<br>SOI MC          | ) A6L-B<br>SOI MOSFETs                                                                                         | AGL-C<br>Ferromagnetic and<br>polycrystalline devices                                                                                                         | AGL-E<br>Cryptographic Processors                                                                                                                                  | A6L-F<br>SAR ADCs and DACs                                       | A6L-G<br>Power Management                                                                                                                | AGL-H<br>mm-Wave Frequency<br>Generation                                                                                                                 |

| 18:40-19:50                          |                                                                                                                |                                                                                                                                                               | FRINGE POSTER BRIEFING SESSION                                                                                                                                     | SESSION                                                          |                                                                                                                                          |                                                                                                                                                          |

| 21:00                                |                                                                                                                |                                                                                                                                                               | WELCOME RECEPTION                                                                                                                                                  | NC                                                               |                                                                                                                                          |                                                                                                                                                          |

|                                      |                                                                                                                |                                                                                                                                                               |                                                                                                                                                                    |                                                                  |                                                                                                                                          |                                                                                                                                                          |

# PROGRAMME AT A GLANCE

Wednesday September 15th, 2010

| Time                                   | ROOM B                                                   | ROOM E                                                                                                                          | ROOM D                                                                                                                                                            | ROOM A                                                             | ROOM C                                                                                                            | ROOM F                                                                                                                              |

|----------------------------------------|----------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|

| 09:00-09:50                            |                                                          | JOINT PLEY<br>SPEAKE                                                                                                            | B1L-A (ROOM A+B)  JOINT PLENARY: Engineering Hope with Biomimetic Microelectronic Systems SPEAKER: Dr. Wentai Liu (University of California Santa Cruz UCSC, USA) | 4+B)<br>mimetic Microelectronic Sy:<br>Iifornia Santa Cruz UCSC, Ü | stems<br>ISA)                                                                                                     |                                                                                                                                     |

| 09:50-10:40                            |                                                          | JOI.<br>SPEAKER:                                                                                                                | B2L-A (ROOM A+B) JOINT PLENARY: Energy Harvesting - from Devices to Systems SPEAKER: Dr. Yiannos Manoli (IMTEK - University of Freiburg and HSG-IMIT)             | 4+B)<br>from Devices to Systems<br>ersity of Freiburg and HSG-     | -IMIT)                                                                                                            |                                                                                                                                     |

| 10:40-11:20                            |                                                          |                                                                                                                                 | COFFEE BREAK                                                                                                                                                      |                                                                    |                                                                                                                   |                                                                                                                                     |

| 11:20-13:00 B3L-B<br>Simula<br>devices | ) B3L-B<br>Simulation of advanced silicon<br>devices     | B3L-C<br>Photodetectors                                                                                                         | B3L-D<br>Silicon and Gallium Nitride<br>power devices                                                                                                             | B3L-F B3L-C TDCs and Timing Circuits Sensors                       | B3L-G<br>Sensors                                                                                                  | B3L-H<br>Power Amplifiers                                                                                                           |

| 13:00-14:50                            |                                                          |                                                                                                                                 | LUNCH                                                                                                                                                             |                                                                    |                                                                                                                   |                                                                                                                                     |

| 14:50-15:50 B4L-B<br>Modeli<br>stress  | ) B4L-B<br>Modeling of temperature and<br>stress impacts | B4L-C<br>Advanced FET<br>characterization                                                                                       | B4L-D<br>Phase Change Memories                                                                                                                                    | ESSCIRC PLENARY: Anal SPEAK                                        | B4L-A (ROOM A)  f: Analog Mixed-Signal Circuits in Advanced Technology SPEAKER: Dr. Ian Young (Intel Corporation) | B4L-A (ROOM A) ESSCIRC PLENARY: Analog Mixed-Signic Circuits in Advanced Nano-scale CMOS SPEAKER: Dr. Ian Young (Intel Corporation) |

| 15:50-16:50                            |                                                          | B5L-A (ROOM B) ESSDERC PLENARY: High Power LEDs for Solid State Lighting SPEAKER: Dr. Berthold Hahn (Osram Opto Semiconductors) | lid State Lighting<br>emiconductors)                                                                                                                              | B5L-F<br>Amplifiers II                                             | B5L-G<br>Circuits for Implantable mm-Wave Receivers<br>Devices                                                    | B5L-H<br>mm-Wave Receivers                                                                                                          |

| 16:50-17:20                            |                                                          |                                                                                                                                 | COFFEE BREAK                                                                                                                                                      |                                                                    |                                                                                                                   |                                                                                                                                     |

| 17:20-18:40 B6L-B<br>Leakag            | ) B6L-B<br>Leakage current and traps                     | B6L-C<br>Tunneling FET devices                                                                                                  | B6L-E<br>Memories                                                                                                                                                 | B6L-F<br>Pipeline ADCs                                             | B6L-G<br>Biomedical Applications RF Building Blocks                                                               | B6L-H<br>RF Building Blocks                                                                                                         |

|                                        |                                                          |                                                                                                                                 |                                                                                                                                                                   |                                                                    |                                                                                                                   |                                                                                                                                     |

# PROGRAMME AT A GLANCE

GALA DINNER

21:00

# PROGRAMME AT A GLANCE

# PROGRAMME AT A GLANCE

Thursday September 16th, 2010

| Time                           | ROOM B                                                                                                                                               | ROOM E                                                                | ROOM D                                                                                                                            | ROOM A                                                | ROOM C                                                                                                      | ROOM F                                                                                                                                                                                                          |

|--------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 09:00-09:20                    |                                                                                                                                                      | JOINT PLEI                                                            | C1L-A (ROOM A+B) JOINT PLENARY: Technical and Economical Trends in Wireless Applications SPEAKER: Dr. Martin Zander (ST Ericsson) | +B)<br>Frends in Wireless Applicat<br>r (ST Ericsson) | ions                                                                                                        |                                                                                                                                                                                                                 |

| 09:50-10:40                    |                                                                                                                                                      | JOINT PLE                                                             | C2L-A (ROOM A+B) JOINT PLENARY: FDSOI: From Materials to Devices and Circuit Applications SPEAKER: Dr. Carlos Mazuré (SOITEC)     | +B)<br>evices and Circuit Applicat<br>uré (SOITEC)    | ions                                                                                                        |                                                                                                                                                                                                                 |

| 10:40-11:20                    | 0                                                                                                                                                    |                                                                       | COFFEE BREAK                                                                                                                      |                                                       |                                                                                                             |                                                                                                                                                                                                                 |

| 11:20-13:00 C3L-B<br>Nanow     | ) C3L-B<br>Nanowire Transistors                                                                                                                      | C3L-C<br>Device steep slope and<br>leakage                            | C3L-D<br>Advanced Memories                                                                                                        | C3L-F<br>Oversampled ADCs                             | C3L-G<br>DC/DC Converters                                                                                   | C3L-H<br>Wireless Communications                                                                                                                                                                                |

| 13:00-14:50                    | 0                                                                                                                                                    |                                                                       | LUNCH                                                                                                                             |                                                       |                                                                                                             |                                                                                                                                                                                                                 |

| 14:50-15:50 C4L-B Chann Engine | ) C4L-B<br>Channel and Gate Stack<br>Engineering                                                                                                     | C4L-C C4L-D Simulation of III/V devices Charge Trap NAND Flash        | C4L-D<br>Charge Trap NAND Flash                                                                                                   | ESSCIRC PLENARY: Ultra L<br>SPEAKER: Dr. David Ruffi  | C4L-A (ROOM A) ow Power and Miniaturize and WSN Applications eux (Swiss Center for Elect CSEM, Switzerland) | C4L-A (ROOM A) ESSCIRC PLENARY: Ultra Low Power and Miniaturized MEMS-based Radio for BAN and WSN Applications SPEAKER: Dr. David Ruffieux (Swiss Center for Electronics and Microtechnology CSEM, Switzerland) |

| 15:50-16:50                    | C5L-A (ROOM B) ESSDERC PLENARY: Trends & Perspectives for Electrical Characterization & Reliability Assessment SPEAKER: Dr. Guido Groeseneken (IMEC) |                                                                       | C5L-E<br>Emerging Memories                                                                                                        | C5L-F<br>mm-wave radar and<br>imaging                 |                                                                                                             | C5L-H<br>UWB Communications                                                                                                                                                                                     |

| 16:50-17:20                    | 0                                                                                                                                                    |                                                                       | COFFEE BREAK                                                                                                                      |                                                       |                                                                                                             |                                                                                                                                                                                                                 |

| 17:20-18:40 c6L-B<br>Analyt    | ) C6L-B<br>Analytical/compact models                                                                                                                 | C6L-C Cetromechanical Devices Circuit Design in Emerging Technologies |                                                                                                                                   | CGL-F<br>Signal Processing<br>Platforms               |                                                                                                             | C6L-H<br>Optical Communications                                                                                                                                                                                 |

|                                |                                                                                                                                                      |                                                                       |                                                                                                                                   |                                                       |                                                                                                             |                                                                                                                                                                                                                 |

#### **ORGANIZATION COMMITTEE**

Conference Chairs José L. Huertas Díaz

IMSE-CNM-CSIC

Ángel Rodríguez-Vázquez

IMSE-CNM-CSIC

Ángel Rodríguez-Vázquez

IMSE-CNM-CSIC

Manuel Delgado-Restituto

ESSCIRC TPC Chairs IMSE-CNM-CSIC

Karin Halonen

Helsinki University of Tech-

nology

Francisco Gámiz

University of Granada

ESSDERC TPC Chairs Andrés Godoy

University of Granada Michael Östling, Royal Ins.

Tech./KTH

**Tutorials & Workshops**

Chairs

Manuel Delgado-Restituto

IMSE-CNM-CSIC

Andrés Godoy

University of Granada

#### LOCAL ORGANIZATION COMMITTEE

#### CONFERENCE VENUE CHAIRS

Dr. Ricardo Carmona, IMSE-CNM-CSIC

Dr. Santiago Sánchez-Solano, IMSE-CNM-CSIC

Dr. Carlos Sampedro, University of Granada

#### COMPUTER AND COMMUNICATION INFRASTRUCTURE

#### & ADVERTISING CHAIRS

Dr. Gustavo Liñán-Cembrano, IMSE-CNM-CSIC

Dr. Rafael Castro-López, IMSE-CNM-CSIC

Dr. Noel Rodríguez, University of Granada

#### **PUBLICATION CHAIRS**

Dr. Oscar Guerra, IMSE-CNM-CSIC / University of Sevilla

Prof. Francisco Jiménez, University of Granada

Prof. Gloria Huertas, IMSE-CNM-CSIC / University of Sevilla

Prof. Rocío del Río, IMSE-CNM-CSIC / University of Sevilla

#### LOCAL ARRANGEMENT CHAIRS

Prof. Diego Vázquez, IMSE-CNM-CSIC / University of Sevilla

Prof. Carlos Sampedro, University of Granada

Dr. Piedad Brox. IMSE-CNM-CSIC / University of Sevilla

#### FINANCE CHAIR

Prof. Antonio Acosta, IMSE-CNM-CSIC / University of Sevilla

#### LOCAL ORGANIZATION

#### Isbilva Travel

Avda. Américo Vespucio s/n

Isla de la Cartuia 41092 Sevilla, Spain

Phone: +34 95 499 10 68 Fax: +34-954990193

isbilva@nervionviaies.com

#### **Local Secretariat**

Mrs. Susana Pazo, susanapazo@esscirc2010.org

#### **CONFERENCE SECRETARIAT**

#### Instituto de Microelectrónica de Sevilla IMSE-CNM-CSIC

Avda. Américo Vespucio s/n Isla de la Cartuja

41092 Sevilla, Spain

Phone: +34 95 446 66 66 Fax: +34-954466669

info@esscirc2010.org

#### STEERING COMMITTEE

William Redman-White

Sorin Cristoloveanu

Cor Claeys Stephen Hall Thomas Skotnicki Ralf Brederlow

Franz Dielacher

Christian Enz

Hannu Tenhunen

Roberto Bez

Roland Thewes

Gaudenzio Meneghesso Doris Schmitt-Landsiedel

Klaas Bult

Athanasios Dimoulas Kazunari Ishimaru (Chair) NXP

(Vice Chair) ENSERG-IMEP (Permanent Secretary) IMEC

University of Liverpool STMicroelectronics Texas Instruments Infineon

CSEM

KTH Stockholm Numonyx TU Berlin

University of Padova

Technical University Munich Broadcom Corporation

NCSR DEMOKRITOS

Toshiba America Elect.

Comp.

#### **ESSCIRC TECHNICAL PROGRAMME COMMITTEE**

Eduard Alarcón UPC

Pietro Andreani Lund U.

Peter Baltus CWTE

Andrea Baschirotto Univ Lecce

Jean Baptiste Begueret IMS-Bordeaux

Didier Belot ST

Roc Berenguer CEIT

Marco Berkhout NXP

Amine Bernak HK Univ. Sci. & Tech.

Andrea Bevilacqua Univ. Padova

Alexis Birbas Univ. Patras

#### **ESSCIRC TECHNICAL PROGRAMME COMMITTEE**

ST Bertrand **Borot**

Ralf Brederlow ΤI

Werner Brockherde Fraunhofer IMS

Erik TU Denmark Bruun

Klaas Bult Broadcom

HK Univ. Sci. & Tech. Howard Cam Luong

Univ. Pavia Rinaldo Castello

Andreia Cathelin ST

Gert Cauwenberghs ST

Sudipto Chakraborty ΤI

Anantha Chandrakasan MIT

Craninckx **IMEC** Jan

Jan Crols Ansem

Dedic Fujitsu Micro lan

Wim Dehaene KU Leuven

**IMSE-CNM-CSIC** Manuel Delgado-Restituto

Andreas Demosthenous UCL

Yann Deval IXL Univ. Bordeaux

Dielacher

Christian Enz **CSEM**

**Tobias** Gemmeke IBM Boeblingen

Friedel Gerfers Acquantia

Giuseppe Gramegna **CSR**

Christoph Hagleitner IBM Zurich

Kari Halonen Helsinki Univ. Tech

Haralabidis Broadcom Nikos

Infineon

Franz

#### **ESSCIRC TECHNICAL PROGRAMME COMMITTEE**

Ralph Hasholzner Infineon

Helfenstein NXP Zurich Markus

Robert Henderson Univ. Edinburgh

Henzler Stephan Infineon

Hernández Univ. Carlos III Madrid Luis

ETH Zurich Qiuting Huang

IMEC-NL Jos Huisken

Jed Hurwitz Gigle Semi, Edinbugh

Nobuyuki Itoh Toshiba

David Johns **U** Toronto

Andreas Kaiser ISEN Lille

Maher **EPFL** Kayal

Peter Kennedy University of Cork

Columbia Univ. Peter Kinget

Kokubo Hitachi Masaru

Per Larsson-Edefors Chalmers Univ. Technol

Domine NXP Research Leenaerts

Lian Nat. Univ. Singapore Yong

TU Delft

Univ. Pavia

Antonio Liscidini Univ. Pavia

Kofi Makinwa TU Delft

Long

Malcovati

Franco Maloberti Univ. Pavia

**Yiannos** Manoli Micro. Ini Freiburg

Rui Martins Univ. Macao

Hiroshima Univ. Hans Juergen Mattausch

John

Piero

#### **ESSCIRC TECHNICAL PROGRAMME COMMITTEE**

Sven Mattisson Ericsson

Peter Mole Intersil

Dominique Morche CEA/LETI

Miki Moyal Intel

Paul Muller Mediatek UK

Bram Nauta Univ. Twente

Tobias Noll RWTH Aachen

Frank Op 't Eynde Audax-Technologies

Ltd

NXP

TU Graz

Xilinx Dublin

Yorgos Palaskas Intel

Yannis Papananos NT Univ. Athens

Christos Papavassiliou Imperial College

Michiel Pertijs TU Delft

Ullrich Pfeiffer Uni. Wuppertal

Christian Piguet CSEM

Pineda

Pribyl

Quinn

José

Wolfgang

Patrick

Rüdiger Quay Fraunhofer IAF

Bill Redman-White NXP

Patrick Reynaert KU Leuven

Ángel Rodríguez-Vázquez Univ. Sevilla

Arthur van Roermund TU Eindhoven

Albrecht Rothermel Univ. Ulm

Stefan Rusu Intel

Takayasu Sakurai Univ. Tokyo

#### **ESSCIRC TECHNICAL PROGRAMME COMMITTEE**

Willy Sansen KU Leuven

Rahul Sarpeshkar MIT

Mohammad Sawan Polytechnique Montral

Doris Schmitt-Landsiedel TU Munich

Tadashi Shibata Univ. Tokyo

Doug Smith SMSC

Michiel Steyaert KU Leuven

Jon Strange Mediatek Wireless

Hannu Tenhunen Royal Inst Technol

Roland Thewes TU Berlin

Marc Tiebout Infineon

Janez Trontelj Univ. Ljubljana

Andrei Vladimirescu UC Berkeley

Piet Wambacq IMEC

Bernhard Wicht TI

Andreas Wiesbauer Infineon

Changsik Yoo Hanyang Univ.

Yue Ping Zhang Nanyang Tech. Univ.

Horst Zimmermann TU Vienna

# **WELCOME TO SEVILLA**

Seville, rich millenary heiress of different cultures that settled along the shores of the Guadalquivir River, preserves and pampers its world famous monumental architecture. At the same time it proudly and brilliantly treasures mysterious secrets that romantic authors attempted to release in mythical works such as Carmen, The Barber of Seville or Don Juan, amongst many others.

Nonetheless, the Seville that we wish to introduce to you today is a synopsis of the values of its past heritage and modernity of its present reality. Such a symbiosis holds the city's historical character which offers contemporary infrastructures which convert the city into a first class tourist destination, not just for the individual tourist but also for the business person attending conferences or incentive trips.

#### THE CATHEDRAL AND THE GIRALDA

"Let us create such a building that future generations will take us for lunatics". That's what churches authorities repudetly agreed back in 1401. And they certainly got themselves the big and magnificent Cathedral, one of the largest catholic churches in the world: the main building is 126m long and 83m wide. The original mosque's beautiful minaret (for the cathedral was built over the main mosque that fell to the christians in 1248), La Giralda, still stands on its eastern side, but the cathedral's bulky exterior gives few other hints of the treasures within.

Price per person: 8€ (general ticket)

Hours: Mon-Sat: 11am - 5pm. Sun: 4.30pm - 6pm

Phone: (+34) 95 421 49 71

#### **A**LCÁZAR

Residence of many generations of kings and caliphs, the notto-be-missed Alcázar is an intriguing, beautiful complex of gardens, patios, and royal rooms, and it is intimately associated with the lives and loves of many Muslim and Christian rulers, above all Pedro I of Castilla, who was known as Pedro

# **WELCOME TO SEVILLA**

El Cruel and Pedro El Justiciero (the Cruel and the Justicedispenser) depending which side of him you were on.

Price per person: 7,5 € (general ticket) Hours: Mon-Sun: 9.30am - 7pm Phone: (+34) 95 450 23 23

#### SANTA CRUZ, THE CENTRO AND THE ARENAL

Santa Cruz is Seville's medieval Judería (Jewish quarter), today a tangle of quaint, winding streets and lovely plantdecked plazas perfumed with orange blossom. Plaza de Santa Cruz, Plaza Doña Elvira, the 17th-century Hospital de los Venerables Sacerdotes, are spots the visitor won't want to miss here. The real centre of Sevilla, El Centro, is densely packed with narrow streets and broken up by squares and streets (Calle Sierpes, Casa Pilatos, Plaza del Salvador....) around which the city's life has revolved for aeons. The Arenal, a short walk from the Cathedral, brings the visitor to the Río Guadalquivir. Seville's most interesting sights here include the Torre del Oro (a 13th-century islamic watch tower), Plaza de Toros (the bullring, one of the most handsome in Spain and probably the oldest), the Hospital de la Caridad and the Museo de Bellas Artes (Fine-Arts Museum), which is the second Art Gallery in the country.

#### **CLIMATE**

Seville has a Mediterranean weather due to the oceanic influences nearby. In the winter the temperatures are mild, and in the summer the weather is hot. Precipitation varies along the year, concentrated in the period October to April. December is the wettest month, and the coldest are January and February. June, July and August are the hottest months. The weather in Seville in September is usually warm. It is sunny almost every day. First rains are late September or

early October and rarely last more than a day or two. In that season of the year, the days are long: the sun rises around 8.00am, and sets around 8.30 pm.

#### **FAST FACTS**

Country: Spain / España

Status: city / capital of Andalusia

Population: 720,000 in the city + another 400,000 in its out-

skirts

Language: Spanish

Time zone: UTC+2 at summer time (March 28 to October 31),

UTC+1 at winter time (From October 31)

Country dialling code: +34

Telephone area code for Seville: 95

**Currency:** Euro is the official currency of Spain. Euro (€) = 100 cents. Notes are in denominations of €500, 200, 100, 50, 20, 10 and 5. Coins are in denominations of €2, 1 and 50, 20, 10, 5, 2 and 1 cents. Money can be taken from cash machines (ATMs) which accept most international cards.

Health and security:

Emergency service (Fireman, police, civil protection, sanitary emergency) phone number: 112

**National police:** emergency telephone number: 091 **Local police:** emergency telephone number: 062

Medical emergencies: emergency telephone number: 061

**Tipping:** tipping in Spain is not obligatory but it is common to leave some change or to give a tip of 5–10%. There are no added service charges on the final bill at any hotel restaurant, or bar...

**Electricity:** 220 volts, 50 Hz - round two-pin plugs are used **Measures:** Weight measured in kilograms, distances measured by the metric system, temperature measured in degrees Celsius

**Tourist Office:** Paseo de las Delicias, 9 (Costurero de la Reina) 41012 Sevilla. Phone: +34 95 423 44 65

Seville tourism information can be found at www.turismosevilla.org and www.andalucia.org

#### **PHARMACIES**

A chemist's or drugstore is known as a Farmacia and they can be identified by a large green or red cross sign outside. They tend to keep the same working hours as other shops and if closed, usually display a sign indicating the nearest pharmacy that is open. As well as selling prescription medicines, they also offer free advice about minor injuries or ailments and they will happily suggest non-prescription treatments. Usually open from 9.30am to 1.30pm, and from 4.30am to 8.00pm. Besides you can find pharmacies that

# **WELCOME TO SEVILLA**

open 24 hours. Pharmacies follow a rolling late-hour schedule, which is published in the newspapers and the internet, and is posted at all pharmacies.

#### Hours of Business/Shops in Seville

Most offices in Seville open at 9.00 am and many close for a couple of hours in the afternoon, although this varies with companies. The most common business time-table is from Monday to Friday, from 9.30am to 1.30pm, and from 5.00pm to 8.00pm. Many shops also open on Saturdays from 9.30am to 1.30pm. Big shopping centres and department stores open from 10.00am to 9.00pm or 10.00pm uninterruptedly, except Sundays and local holidays.

#### **BANKS OPENING TIMES:**

Banks are generally open Monday-Friday from 8.30am to 2.00pm, and sometimes on Saturday from 8.30am to 1.00pm.

#### **CURRENCY EXCHANGE**

There are many places to exchange currency, the banks being the ones with best rates. There are also foreign exchange outlets in the airports and even in some hotels and restaurants, although the rates are usually not so favourable. Withdrawing money at a cash point (ATM) is often the most convenient and economic way to obtain Euros and there are ATMs all over the city. Many are located inside banks or in their facades.

#### CREDIT CARDS, TRAVELLERS CHEQUES

Credit cards are widely accepted at establishments throughout Seville and these include Visa, EuroCard, Access, Master-Card and American Express. In some stores, you may be asked to enter your PIN (Personal Identification Number) into a keypad for security purposes. Some shops do not accept credit card payment for a small monetary amount. Travellers cheques, accompanied by a passport, are also accepted in most hotels, restaurants and shops.

#### ATMs (AUTOMATIC BANKING MACHINE)

There are ATMs almost everywhere, and most support Visa/Plus, Cirrus, and other popular systems. Just look for the signs next to the ATM or on the display itself. ATMs are easy to use here and all offer English as well as other languages.

#### IVA (VAT) REFUND

How to get IVA (VAT) back on shopping: If a buyer's residence is outside the European Union, then he/she can claim back the tax on purchases, as long as they amount for more than 90.15 Euro in each establishment. In order to do so, you

# **WELCOME TO SEVILLA**

should ask for a tax-free receipt, wherever you see the Spain Refund Tax-free Shopping logo, at the point of sale. The Tax-Free cheque must be stamped, always before the check-in. Show the goods to customs when leaving the country. You can claim your money in the SPAIN REFUND cash agents in airports and borders. (Tax free Spain refund information www.spainrefund.com, www.globalrefund.com)

#### **CURRENCY CHOICE LOGO**

The Currency Choice logo next to a credit card terminal means that there you can pay by credit card in your own national currency. The amount on the receipt is the sum that will be debited to your bank. No hidden fees, no surprises when you get back home.

#### **VISA INFORMATION**

Anyone wishing to travel to and enter Spain must have a valid passport and/or the appropriate Spanish Visa. We recommend contacting your local Spanish consulate or Embassy for more information on these requirements.

For further information about Sevilla, please check www.infosevilla.com

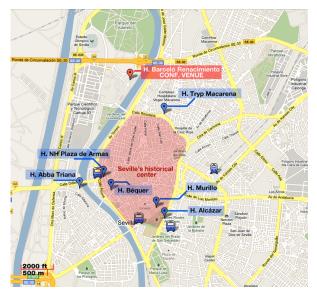

The conferences, tutorials and workshops will be held at the:

#### BARCELÓ RENACIMIENTO HOTEL

Isla de la Cartuja, s/n E-41092

The avant-garde Barceló Renacimiento\*\*\*\*\* is a modern, top-quality hotel located in Seville, on the Island of La Cartuja, on the banks of the Guadalquivir river, that is today home to the Cartuja scientific and technologic park. It is the best equipped hotel in the city to accommodate groups, conferences, congresses and incentive trips, boasting its own 25-room Convention Center.

Conveniently located, just a few minutes away from Seville's historic center, the high-speed AVE train station and the airport close by, is an attractive option for both business travelers and people interested in urban sight-seeing.

Barceló Renacimiento's facilities include 25 meeting rooms and 2 atriums for events. The Convention Center Gran Sevilla was opened in 2002 and it provides fully equipped 1,024m2 ideal for any kind of event. It can be turned into 3 independent rooms where natural light is very important. Besides, there is an exhibition area of 800m2.

Barceló Renacimiento hotel is member of the International Congress and Conventions Association (ICCA).

#### LOCATION

COORDINATES:

LAT: 37° 24´ 35´´ N LONG: -5° 59´ 43´´ W - E

Distance to the city centre: 1-2 kilometres.

Distance to the airport: 10 kilometres.

Train station: 20 minutes.

Near by City bus lines C1 and C2.

A range of hotels (see map below) to suit all budgets and requirements are also within a short distance of the meeting venue.

#### How to reach the venue

#### **BY CITY BUS**

There is a good city bus service from/to the conference site to/from the city center (it takes around 10-20 minutes). Walking distance to bus stop: 3-5 minutes.

Please, see below section "Getting around" for further information.

#### By Taxi

Please, see section below on "Getting around" for further information.

#### RAILROAD/RAILWAY

The railroad transportation system connects all major urban centers. The Santa Justa train station serves as an important hub for connections between the Andalusia's main cities and all of the autonomous regions of Spain and Europe. AVEs (high speed trains) connect to/from Cordoba (around 30€ to 50€, 40 minutes), Malaga (36€, 2 hours), Madrid (usually 64€ to 70€, 2½ hours) or Barcelona (80€ to 250€ (  $5\frac{1}{2}$  hours).

In addition to the AVE service, this modern station concentrates all railway traffic, with trains to various towns of the province, to all the capitals of Andalusia and to other Spanish cities such as Barcelona, Valencia, Alicante and Cáceres. The Santa Justa Train Station is located at Avda. Kansas City s/n. 41007 Sevilla, Information phone +34 902 320 320. International information phone: +34 902 243 402

For further information about train services and other train and destinations please visit the www.renfe.es

#### ROADS

Highway and access roads and rapid beltways provide precise connections to all neuralgic points of the city and its surroundings. Seville has now become one of Spain's best connected cities by road, with highways connecting all Andalusia's main cities as well as Madrid and Portugal. Main access roads are the A-92, N-IV, A-4, and A-49.

#### **GETTING AROUND**

#### City Buses:

(Spanish name: autobús) Buses are the cheapest way to get around Sevilla. A single bus ride is 1.20€, but you can buy a voucher with 10 trips (bonobus) from 7€ at a newsstand or tobacco shop. The city bus network is based around four lines- C-1, C-2, C-3, and C-4- which follow circular routes, linking the main transport terminals and the city centre. Four transversal lines and a series of radial lines which lead into the centre from the four points of the compass complete the bus network.

You can pick up a bus route map, the Guía del Transporte Urbano de Sevilla, from tourist offices or from information booths at major stops (including Plaza Nueva, Plaza de la Encarnación and Avenida de Carlos V).

Information Phone: 010 (press 5) Web Site: www.tussam.es

On the other hand, Seville has two bus stations, each providing services to separate cities:

-Prado de San Sebastián, just southeast of the Barrio de Santa Cruz, provides bus services to cities of Andalusia. Address: Manuel Vázquez Sagastizábal s/n. - Sevilla. Phone: +34 95 441 71 11

-Plaza de Armas, by the Cachorro's bridge, connects with the rest of Spain, the Province of Huelva, and Portugal. Address: Avenida del Cristo de la Expiración, s/n. - Sevilla. Phone: +34 95 490 80 40

#### Sightseeing tour buses:

Tour buses can be a great way to get around Seville. You have the option of traveling the full circuit and getting an overview of what to expect in the city or get on and off as many times as you want, seeing the sights as you go.

Web site: www.busturistico.com

#### Taxis:

Taxi stops are located on several central streets and squares. However, taxi can be hailed any place in the city when they show the *libre* (free) sign or a green light.

Many of the short cab rides cost between 3-6€. From the airport to the city center or the opposite there is now a flat rate. The fee is 17€ during the day and 20€ during holidays, Sundays or night (after 10pm).

Phones: +34 95 467 55 55 / +34 95 458 00 00 / +34 95 462 22 22

Web sites: www.taxisevilla.es, www.taxigiralda.es

#### Subway and tram:

(Spanish name: *metro*) Seville's subway system has only one line that goes from the west to the south part of the city and surrounding suburbs. A single ride is 1.30€.

(Spanish name: tranvía metro centro) (T1) is a surface tram by the center of Seville that connects Plaza Nueva to Prado de San Sebastián bus station, with a total of 1.3km. This route covers the pedestrian area in the city center.

Web site: www.metrodesevilla.org

#### Bicycle:

(Spanish name: bicicleta) Sevici is the name of a community bicycle program in Seville. Its purpose is to cover the small and medium daily routes within the city in a climate friendly way. More than 250 stations and 2500 bikes will be available. The stations are situated throughout the inner-city with a distance of around 200 metres between each one, with many situated next to public transport stops to allow for intermodal use. The bikes can be borrowed from, and returned to, any station in the system, making it suitable for one way

travel. Each station has between 10 and 40 parking slots to fix and lock the bicycle.

There is a short term subscription for tourists with an unlimited number of journeys during 7 consecutive days (a deposit of 150€ is mandatory).

Web site: www.sevici.es

#### Other ways:

**On foot:** The city center of Seville is not very large and it is easy to walk to all the tourist spots, a lot of fun to walk around. The centre has almost become completely car-free.

Horse-Drawn carriage tour: it is very typical way to get around Seville. You have the opportunity to get more information and register for this tour at a reduced price for ESSCIRC/ESSDERC attendees at: http://www.esscirc2010.org/registro/excursiones/registration\_form.php

River cruises along the Guadalquivir River: the emblematic Andalusian river, the Guadalquivir is the only navigable river in Spain. You have the opportunity to get more information and register for this cruise at a reduced price for ESSCIRC/ESSDERC attendees at: http://www.esscirc2010.org/registro/excursiones/registration\_form.php

#### Sevilla Tourist Card

Sevilla Card, the Seville tourist card, will help you discover the city and enjoy your stay and save money. Its price is from 29€ to 50€ per day. Some advantages with the card are:

- -Free admission to most museums and monuments in the city and environs.

- -Unlimited use of sightseeing buses.

- -Boat rides on the Guadalquivir River.

- -Isla Mágica Theme Park.

- -Besides you will be able to enjoy discounts in shops, restaurants, shows and leisure centres for adults and children.

- -Guide/map with information about museums, services included and participating establishments.

- -A free "traditional tapa" as well as a drink.

Web site: www.sevillacard.es

# **CONFERENCE INFORMATION**

#### LANGUAGE

The official language of the Conference is English.

#### **WEBPAGES**

ESSCIRC 2010 webpage: www.esscirc2010.org ESSDERC 2010 webpage: www.essderc2010.org

#### **NAME BADGES**

All participants and accompanying persons are asked to wear their name badges in a visible place. Entrance to sessions is restricted to registered delegates only. Entrance to meeting halls, poster and exhibition areas is granted to badge holders.

#### SPEAKERS BRIEFING

Authors should meet their chairperson in the session room 15 minutes ahead the respective sessions.

#### INTERNET ACCESS

Wireless internet access will be available at the conference venue without charge.

#### CONFERENCE PROCEEDINGS

All participants will receive a copy of either the ESSDERC or the ESSCIRC Proceedings and a CD containing the accepted papers for both.

#### **BEST PAPER AWARD**

Papers presented at the conferences will be considered for the Best Paper Award and for the best "Young Scientist" Paper Award. The selection will be based on the results of the paper selection process and the judgment of the conference participants. The award delivery will take place at ESS-CIRC/ESSDERC 2011.

#### INSURANCE DISCLAIMER

Participants are responsible for their own insurance. The organizers cannot take responsibility for any accident, loss or damage to participants or their property during the event.

#### COMPLAINTS

While we hope that your time at the conference is enjoyable, if you encounter a problem during your stay, please report it to the registration desk as soon as possible. The conference team will make every effort to rectify the issue.

# **CONFERENCE OVERVIEW**

In addition to contributed papers and plenary lectures, the event will include tutorials, exhibits and satellite workshops to be organized before and after the conference.

An attractive social program will complement the event, featuring a welcome reception, a gala dinner with awards ceremony, and excursions.

#### SCHEDULE AT A GLANCE

### Monday, September 13th, 2010

**Tutorials**

#### TUESDAY, SEPTEMBER 14TH, 2010

Conference Opening Technical Sessions Welcome Reception

#### WEDNESDAY, SEPTEMBER 15TH, 2010

Technical Sessions Gala Dinner

#### THURSDAY, SEPTEMBER 16TH, 2010

Technical Sessions

#### FRIDAY, SEPTEMBER 17TH, 2010

Workshops

#### THE AIM OF THE CONFERENCE

The aim of the ESSCIRC conference is to provide an annual European forum for the presentation and discussion of recent advances in solid-state circuits.

#### **GENERAL SCOPE OF THE CONFERENCE**

ESSCIRC and its sister conference ESSDERC, which deals with solid-state devices and technologies, are governed by a single Steering Committee. The increasing level of integration for system-on-chip (SoC) design made available by advances in silicon technology is stimulating more than ever before the need for deeper interaction among technologists, device experts, and circuit and system designers.

While keeping separate Technical Program Committees, ESS-CIRC and ESSDERC will share Plenary Keynote Presentations bridging both communities. Attendees registered for either conference are encouraged to attend any of the scheduled parallel sessions.

# **CONFERENCE OVERVIEW**

#### THEMES OF THE CONFERENCE

The conference's core themes are set out below. The programme committee also welcomes novel contributions from other related areas.

#### **ANALOGUE CIRCUITS**

Amplification stages, Power amplifiers for audio applications, Continuous- and discrete-time filters, Switched-capacitor circuits, Comparators, Nonlinear circuits, Voltage/current references, HV circuits.

#### **DATA CONVERTERS**

Nyquist rate converters, Oversampled A/D and D/A converters, Sample-and-hold circuits, A/D and D/A converter calibration and error correction circuits, Adaptive and smart data converters.

#### RF AND MM WAVE

RF/IF/analog baseband circuits, LNAs, Mixers, Power amplifiers, IF amplifiers, Power detectors, Modulators-Demodulators, VCOs, PLLs, Frequency synthesizers, Frequency dividers, Integrated passive components.

#### WIRELESS AND WIRELINE COMMUNICATION CIR-CUITS AND SYSTEMS

Receivers/transmitters/transceivers for wireless systems, Base stations and handsets, Advanced modulation systems, TV/radio/satellite receivers, Radar.

#### SENSORS, IMAGERS AND MEMS

Sensor subsystems and interfaces, Accelerometers, Temperature sensing, Imaging and smart imaging chips, Vision systems on chip, AMOLED, MEMs subsystems, RF MEMs.

#### **DIGITAL CIRCUITS**

Digital circuit techniques, I/O and inter-chip communication, Reconfigurable digital circuits, Clocking, Arithmetic building blocks.

#### PROCESSORS, MEMORIES AND INTERFACES

Memories, Microprocessors, DSPs, Gigabit serial links, Clock data recovery, Equalization, Memory interfacing, Bus interfacing, Multi-rate link IC ´s.

# BIO-MEDICAL AND BIO-ELECTRONIC CIRCUITS & SYSTEMS

Implantable electronic ICs, Bio-electronic integrated systems, Bio-medical imagers, Bio-MEMS integrated systems, Lab-on-chip, Wireless body area networks.

#### CIRCUIT & SYSTEMS IN EMERGING TECHNOLO-GIES

Digital, analogue and mixed-signal circuits using emerging devices such as: Multi-gate MOS- FETs (Double-Gate MOS-

# **CONFERENCE OVERVIEW**

FETs, FinFETs, Triple-Gate MOSFETs); Flexible electronic components; Organic transistors; Nanowires/nanotubes; Quantum devices.

#### POWER MANAGEMENT AND ENERGY SCAVENG-ING

Energy transducers, Power regulators, DC-DC converters, LDOs, Boost converters, Buck converters, LED drivers, Sequencers and supervisors, Green circuits.

# **MEALS AND REFRESHMENTS**

All meals and refreshments will be served at scheduled times during the conference programme.

#### Monday, September 13th, 2010.

Morning refreshments In front of Rooms A+B

Lunch Colón, Cartuja, Atrio I

Afternoon refreshments In front of Rooms A+B

#### TUESDAY, SEPTEMBER 14TH, 2010

Morning refreshments In front of Rooms A+B

Lunch Colón, Cartuja, Atrio I

Afternoon refreshments In front of Rooms A+B

Welcome Reception place to be announced

#### WEDNESDAY, SEPTEMBER 15TH, 2010

Morning refreshments

Lunch

Afternoon refreshments

Gala Dinner\*

In front of Rooms A+B

Colón, Cartuja, Atrio I

In front of Rooms A+B

Convention Centre Sevilla

#### THURSDAY, SEPTEMBER 16TH, 2010

Morning refreshments

Lunch

Afternoon refreshments

In front of Rooms A+B

Colón, Cartuja, Atrio I

In front of Rooms A+B

\*The Gala dinner is included in the registration conference fee. To buy additional tickets, please contact to the registration desk.

Participants with special dietary requirements who have not previously informed about it please contact to the registration desk in order to provide an alternative menu.

# **SOCIAL PROGRAMME**

#### TUESDAY, SEPTEMBER 14TH, 2010

#### WELCOME COCKTAIL

A Welcome reception for ESSDERC-ESSCIRC will be offered. For further details, please visit the conference webpage.

# WEDNESDAY, SEPTEMBER 15TH, 2010 GALA DINNER

A Gala Dinner for ESS-DERC-ESSCIRC will be held at 'Centro de Convenciones y Congresos Sevilla' (Convention Centre Sevilla).

The new Convention Centre Sevilla offers adequate spaces for many different events, spacious reception areas and gardens where enjoy tradi-

tional Spanish food and live entertainment.

Only 15 minutes away from the city of Seville (coaches will be provided to transport participants).

Bus departure at 21:00 from the Barceló Renacimiento Hotel.

To know more about the Centro de Convenciones y Congresos Sevilla, please visit the website at www.centrosevillacongresos.com

# **OPTIONAL LEISURE ACTIVITIES**

#### SIGHTSEEING TOURS AND ACTIVITIES

You have the opportunity to make different sightseeing tours and activities offered at a reduced price for ESSCIRC / ESS-DERC attendees and accompanying persons. To register and get more information, please visit

http://www.esscirc2010.org/registro/excursiones/registration\_form.php

#### ACTIVITIES (13 - 19 SEPTEMBER 2010)

#### **Historic Sevilla**

Departure Days: Wednesday, Friday, Sunday

Duration: 3.5 hours

Departure Point: Hotel or place assigned by the agency

33€ Tax Included

#### Classic Seville - Morning Tour

Departure Days: Monday, Tuesday, Thursday, Saturday

Duration: 3.5 hours

Departure Point: Hotel or place assigned by the agency

33€ Tax Included

#### Artistic Sevilla - Afternoon Tour

Departure Days: Monday, Wednesday, Friday, Sunday

Duration: 3 hours

Departure Point: Hotel or place assigned by the agency

29€ Tax Included

#### Monumental Sevilla - Morning Tour

Departure Days: Monday, Tuesday, Thursday, Saturday

Duration: 3 hours

Departure Point: Main door of the Starbucks cafe - San

Fernando Street 1 (Puerta Jerez)

19€ Tax Included

#### Typical Sevilla

Departure Days: Wednesday, Friday, Sunday

Duration: 3,5 hours

Departure Point: Main door of the Starbucks cafe - San

Fernando Street 1 (Puerta Jerez)

25€ Tax Included

#### Roman City of Itálica - Afternoon tour

Departure Days: Tuesday, Thursday, Saturday

Duration: 4 hours

Departure Point: Hotel or place assigned by the agency

25€ Tax Included

#### Sevilla Night

Departure Days: DAILY

# **OPTIONAL LEISURE ACTIVITIES**

PTIONAL LEISURE ACTIVITIES

Duration: 3 hours

Departure Point: Hotel or place assigned by the agency

45€ Tax Included

#### Granada

Departure Days: Wednesday, Friday, Sunday

Duration: 12 hours

Departure Point: Hotel or place assigned by the agency

110€ Tax Included

#### Cordoba

Departure Days: Tuesday, Thursday, Saturday

Duration: 9 hours

Departure Point: Hotel or place assigned by the agency

85€ Tax Included

#### Jerez & Cádiz

Departure Days: Tuesday, Thursday

Duration: 9 hours

Departure Point: Hotel or place assigned by the agency

94€ Tax Included

#### **Tickets River Cruise along the Guadalquivir**

Departure Days: DAILY Duration: 1 hours

Departure Point: Paseo Alcalde Marqués de Contadero

(Muelle Torre del Oro) 12€ Tax Included

#### Tickets River Cruise + Flamenco Show (AFTERNOON)

Departure Days: DAILY Duration: 3 hours

Duration. 5 hours

Departure Point: Boat: Muelle Torre del Oro / Flamenco:

María Auxiliadora Avenue 18 B

39€ Tax Included

#### Tickets River Cruise + Flamenco Show (NIGHT)

Departure Days: DAILY Duration: 3 hours

Departure Point: Boat: Muelle Torre del Oro / Flamenco:

María Auxiliadora Avenue 18 B

39€ Tax Included

#### Hop On Hop Off Tour Bus

Departure Days: DAILY Duration: 24 hours

Departure Point: Torre del Oro

14€ Tax Included

#### **OPTIONAL LEISURE ACTIVITIES**

#### Sevilla Walking Tour + River Cruise

Departure Days: DAILY Duration: 2.5 hours

Departure Point: Torre del Oro

28€ Tax Included

#### Walking Tour + Horse-Drawn carriage tour

Departure Days: DAILY Duration: 2.5 hours

Departure Point: Plaza de España

48€ Tax Included

#### Romantic Sevilla

Departure Days: DAILY Duration: 2 hours

Departure Point: Plaza de España

75€ Tax Included

#### MUSEUMS IN SEVILLE

Free entry for EU citizens. Non-EU citizens: 1,50 € to the following museums:

-Museo arqueológico de Sevilla (**Archaeological Museum**) http://www.museosdeandalucia.es/cultura/museos/MASE/ ?Ing=en

-Museo de Bellas Artes (Museum of Fine Arts)

http://www.museosdeandalucia.es/cultura/museos/

MBASE/?Ing=en

-Museo de artes y costumbres populares (Museum of Arts and Traditions)

http://www.museosdeandalucia.es/cultura/museos/MACSE/

-Conjunto arqueológico Itálica (Archaeological Ensemble Italica)

http://www.museosdeandalucia.es/cultura/museos/CAI/

-Conjunto arqueológico de Carmona (Archaeological Ensemble Carmona)

http://www.museosdeandalucia.es/cultura/museos/CAC/ ?Ing=en

Non-free entry:

-Monasterio de la Cartuja (Cartuja Monastery) and Centro andaluz de arte contemporáneo (Andalusia Contemporary Art Centre)

http://www.juntadeandalucia.es/cultura/caac/english/frame.htm

1,80€ Visit the monument or to the temporary exhibitions 3,01€ Complete visit

# JOINT PLENARY TALKS

# HIGH PERFORMANCE MIXED SIGNAL: BUSINESS AND TECHNOLOGY

Dr. René Penning de Vries, NXP Semiconductors

René Penning de Vries, NXP Semiconductors, Netherlands Hans Rijns. NXP Semiconductors, Netherlands Maarten Vertregt. NXP Semiconductors, Netherlands

#### Abstract